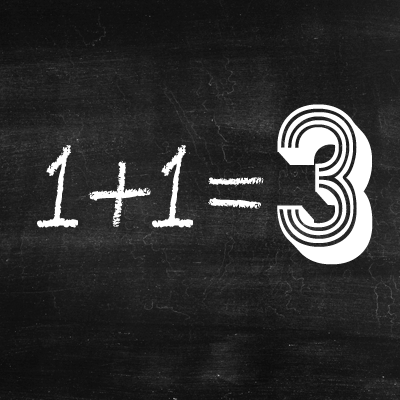

Hello students, please take a seat. I’d like to welcome you to Marketing Mathematics 201. That’s right, compared with other “intro” classes, we have almost 2X the oomph, giving you an estimated 120% more learning with 3/7ths less homework energy expenditure.

If you’ll please look at your syllabus (which, by the way, is 28% shorter than last year’s, while packing in up to 500% more aggregated knowledge) you’ll see that we will have only four effective exams in the course this term (distributed across five discrete tests), reducing exam stress by an estimated 72 thermal units, while simultaneously increasing the accuracy of accomplishment measurement by a staggering 12 effective resolution bits.

Now, just a note before we begin. If any of you are on the “future FPGA marketing” career path, you’re in the wrong room. You’ll need to attend “Advanced Xtreme Marketing Mathematics 767+” on the top floor of the tower in the administrative building.

Let’s get started. First, open your textbooks to the latest Xilinx product tables.

You’ll notice there on the top line that Xilinx device capacity is now quoted in something called “System Logic Cells.” Is that a new one for you? Well, it should be, because until this year “System Logic Cells” was a concept that completely did not exist in the universe.

We’ll use this as an example to highlight Marketing Mathematics Principle #1 (MMP1):

“Make up your own units”

That’s right. If the competitor’s car has 500 horsepower and yours only has 450, just reach into the old toolbox and pull out trusty-old MMP1. Presto! Your engine is now cranking out a remarkable “up to 575 Peak Units of Mule Strength (PUMS).” Your 575 PUMS will blow away their puny 500 HP any day of the week!

So, back to our example, what is a Xilinx “System Logic Cell” anyway?

It appears to be a new unit (defined in 2015 using MMP1) that is equal to “Just enough 6-input LUTs so that our biggest device sounds larger than Altera’s biggest device.” Or, specifically, 2.18 times the number of 6-input LUTs on the chip.

Let’s explain:

Prior to the invention of the “System Logic Cell”, Xilinx product tables referred simply to the “logic cell” which was equal to 1.75 times the number of 6-input LUTs.

If you look on page 2 of your textbook at the “previous version of the Xilinx product tables,” you’ll see that the Xilinx UltraScale XCVU065 had about 650K of these old “logic cells” (which is presumably why it’s called XCVU065 in the first place).

Then, If you look into the details, you’ll then see that the actual number of logic cells reported was 626,640 which, as any marketer worth their salt knows, can be adjusted from 626,640 to 650,000 using Marketing Mathematics Principle #2 (MMP2):

“Always Round Up. A LOT”

NOTE: This is a worthy application of MMP2, with a “round up” of 23,360, which is more than an entire Xilinx Artix-7 XC7A15T device (which boasts a “fully-marketing-inflated” capacity of 16,640 “logic cells”).

However, if you look back at the NEW Xilinx product tables, you’ll find that same old XCVU065 650K device now expanded into a 783K device, thanks to the magic of “System Logic Cells”. That’s right, a 25% increase in claimed capacity with no changes whatsoever to the silicon or the design software. Just Marketing Math Magic that would make the Russian Olympic Team proud.

Xilinx’s largest current device, the XCVU440, which we reviewed in this article back in 2013, prompted this from us:

“The UltraScale families themselves boast some impressive numbers. The largest device in the upcoming Virtex UltraScale family – the VU440 – boasts an incredible 4.4 million “logic cells” (4-input LUT equivalents).”

Well, 4.4 million was certainly a LOT of cells, wasn’t it?

At least, until archrival Altera came along and said that their upcoming Stratix 10 GX/SX devices would have up to 5.5 million logic cells! (The details say it has 5,510,000 “logic elements,” so apparently Altera’s Marketing Mathematicians missed out on MMP2’s “Round UP” principle. Anyway, we digress.)

Oh my, oh my, oh my. What to do? 4.4 million was pretty impressive until 5.5 million came along.

Apparently Xilinx’s answer to “what to do” was to invent the new “System Logic Cell,” bumping the old multiplier from 1.75 up to a more competitive 2.18. Now, the venerable XCVU440 magically ascends from a previously impressive 4.4 million cells to an Altera-beating 5.5 million cells (also featuring an MMP2-eschewing “round down” from a detailed spec of 5,541,000, by the way) with nothing but a wave of the Marketing Mathematics Magic Wand.

Shame on Xilinx, right?

Oh no. Hang on a minute there, super-shamers. There’s more to this story than meets the eye.

Xilinx blew it – not by inflating their product data. Heck, everybody does that. Their big mistake was being so obvious about it and temporarily forgetting Marketing Mathematics Principle #3:

“The First Liar Doesn’t Have a Chance”

That’s right. Never go first in a game of exaggeration. If you don’t understand why, go back to Game Theory 101. We can’t help you here.

You see, it would be easy to fault Xilinx for bumping their claimed capacity from 4.4 million logic cells to 5.5 million system logic cells for the VU440. But really, they had been letting Altera out-exaggerate them by too much for too long.

For the record, the actual number of 6-input LUTs in the respective Xilinx and Altera devices is:

2,532,960 6-input LUTs Xilinx Virtex UltraScale VU440

1,867,680 6-input LUTs Altera Stratix 10 GX/SX 5500

Wait, what?

Yep, you read that right. It looks like Xilinx might really actually have the bigger device.

Altera was already using a whopping 2.95 conversion factor (from 6-input LUTs to “logic elements”). Xilinx apparently simply bumped theirs up “just enough” from 1.75 to 2.18 to make their biggest device “look” bigger. And, clearly, they exercised restraint, because if you measure capacity in actual, real, physical 6-input LUT structures that might possibly be found on the chip, they appear to have significantly more.

Altera, by the way, has a nice footnote in their product table:

“LE counts valid in comparing across Altera devices, and are conservative vs. competing FPGAs.”

We’re not quite sure about the definition of “conservative” in that sentence.

Of course, neither Xilinx nor Altera has anything on their chips actually resembling the “logic elements” or “logic cells” that are used on the product tables. These are all fabricated numbers intended to give some kind of relative capacity compared with years-old devices that used 4-input look-up tables (LUT4s). When both companies made the switch from 4-input LUTs to 6-input LUTs, they couldn’t bear the thought of quoting a number of “cells” or “elements” that might look smaller than their previous generation, so they began giving capacities in mathed-up numbers intended to maintain consistency at the expense of reality.

If you ask us, a more reasonable conversion from 6-input LUTs to 4-input LUTs might be 1.5 (owing to the non-marketing math that 6 is 1.5 times 4). But hey, if Altera wants to use 2.95 and Xilinx wants to use 2.18, who are we to call them out?

And, that gets us to Marketing Mathematics Principle #4, which we’ll discuss tomorrow:

“Never Go Backward.”

Well, we’re out of time. This concludes our Marketing Mathematics lesson for today. If you have any questions or comments, please leave them in the box below.

You should note that Altera is using ALMs, not 6-input LUTs. ALMs contain 2x 4-input LUTs + some logic to fancy combine them + 2 dedicated adder-bits. (At least I assume that Stratix 10 uses the same type of ALM – I could not download meaningful documents because Altera has messed up there homepage…)

So for Altera, a factor of 2x to convert into “classic” 4-input LEs is fair for sure, as they are physically there. If a total factor of 2.95 for the other features is fair? I am not sure, might be very design dependent (do you need a lot of adders?).

For Xilinx, on the other hand, a factor above 2 is surely too high, as a 6-input LUT will seldom replace more than 2 4-input LUTs, but often only 1 (of course also design dependent…).

But when comparing the two discussed parts, for the objective observer it is very clear that the Altera part is “larger”. For the logic, beside above explanation, also the number of logic FFs give some indication (Altera: 7.4M, Xilinx: 5.1M) although they are not very useful by themselves, but also all other metrics like memory, multipliers, etc. are clearly pro-Altera in this question.

On the other hand, as very few people will really require the largest available part, the whole discussion (“who has the largest part”) is quite useless (even more when considering the delivery situation of these parts…). In most applications, the more important question will be how much a given performance and resource requirement will cost you from the respective vendor… (Beside many other considerations like tool quality, etc.) Of course for easy comparison, it would be nice if comparable logic element metrics would be used. This way, I think, a lot of people will be fooled…

(But the much worse thing is the long duration of getting production volume pricing from either vendor… It looks like they urge you to make the part decision before you know pricing. But this is a different story…)

Just under 30 years ago, when the word FPGA had to be explained, a stealth mode company published a paper in Electronics (The leading technical publication of the time). It was called something like Counting Gates and compared how Altera and Xilinx used different calculation methods for their devices. Of course the point was that Actel was going to be open and honest in the way it was going to calculate gates when it announced its products. And naturally, when Actel did announce, Xilinx and Altera both criticised its calculations.

30 years on we are still playing the same games

@tentner, If I were in FPGA marketing, I’d probably point out that one 6-input LUT requires 64 bits while a 4-input LUT requires only 16 bits.

That should justify using a factor of 4 when converting from LUT6 to LUT4, correct?

Therefore, by that simple logic, Altera and Xilinx are both actually being quite conservative…

Kevin