What if you could just… toss it all and start over? (OK, maybe all except the router?)

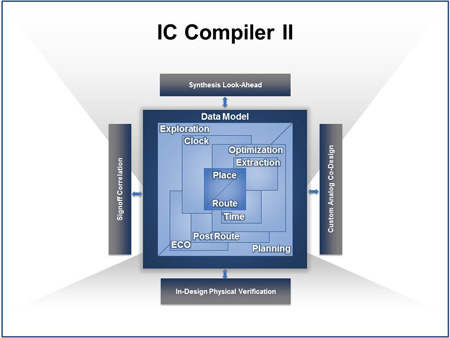

If you’re Synopsys, you now know: you’d end up with IC Compiler II.

They’ve had a good ride with IC Compiler, and they continue to ride that. But things have changed a lot since it appeared on the scene. Requirements and expectations have mushroomed, and they’ve done a lot of new research and acquired a lot of technology (apparently their Magma acquisition fed into this). And so they’ve pretty much replaced everything in IC Compiler except the router.

The new approach pushes planning to a much earlier stage. Engines have been completely redone, with an emphasis on the ability to use multiple processors, which means that more options can be explored. They use that magic number “10x” for many of the speedups. Not only that, but their optimization engines are better at finding a global optimum in an analytical fashion rather than via the alternative: generating a bazillion options and picking the best one.

More specifically, they address the following areas:

- Infrastructure

- Hierarchy is handled natively.

- They have a new timer and extractor that are used consistently throughout.

- They can deal with incomplete data early in the design cycle.

- They’ve implemented an integrated library and management approach.

- Planning

- They’ve implemented adaptive abstraction and modeling.

- They support transparent multiple instances.

- What-if analysis can be done in real time instead of having to compile.

- A floorplan can be automatically synthesized.

- Implementation

- This is where they have the new multi-threaded optimization engine that analytically finds global optima.

- They’ve redone their multi-corner, multi-mode, multi-voltage handling.

- Placement and clock optimization now happen in a single step.

- They’ve completely redone the clock tree synthesis engine.

- They’ve put in place new ways to achieve closure after routing.

At this point, the entire new system isn’t in place yet. They’ve got bits and pieces that they’ve been feeding to a few lead customers to refine things as they approach a mid-year full release.

They will continue to support the original IC Compiler well into the future. They see a gradual shift from one to the other; they’re not going to pull a Microsoft and force everyone over.

You can check out more in their announcement.