Memory has always been a fundamental challenge for the design of digital computers. The quest for the perfect digital storage medium started as soon as digital computers started to appear in the 1940s. Punched cards and paper tape, used in the design of ENIAC in 1945, were clearly too slow and limited. The first fully electronic memory relied on cathode-ray technology in the form of Williams-Kilburn tubes, which were used in the design of the Manchester Baby computer in 1948. These tubes stored a mere handful of bits using phosphor persistence as the storage medium. This technology was borrowed from radar, and the persistence of Williams-Kilburn memory is measured in a scant few seconds, or less. Mercury delay lines, also borrowed from radar, stored bits as a serial string of acoustic pulses and first appeared in the EDSAC computer, which became operational in 1949.

Magnetic core technology, first used in the design of the MIT Whirlwind computer in 1953, quickly replaced Williams-Kilburn tubes and mercury delay lines. Core memory stores data using the extremely persistent characteristics of magnetic hysteresis. As the Computer History Museum has discovered, core memories in long-dormant computers from the 1950s and 1960s hold their programs and data for decades, long after these computers were retired and put into storage. DRAMs, invented by Robert Dennard at IBM in 1966 and successfully commercialized by Intel in 1970, store bits as electric charge in the persistent memory of tiny on-chip capacitors. The DRAM’s appearance in 1970 quickly ended core memory’s 20-year reign.

More than half a century later, and with a tremendous investment in development, DRAMs still rule as the dominant form of digital memory because they offer the best available mix of low cost per bit, high capacity, and fast read/write access times. Despite its long life, DRAM has many shortcomings including a short memory persistence measured in seconds. Back in the 1980s, I was surprised to find that I could restart one of my workstation designs, and, if done quickly enough, the system’s DRAM still held the program for a few seconds after the refresh cycles had ceased. DRAMs, like Williams-Kilburn tubes, require frequent and periodic refresh. The decades-long quest to find a DRAM replacement continues because the DRAM market is extremely attractive. Revenue from DRAM sales currently exceeds $100 billion annually. A replacement semiconductor memory technology might capture some or all of that revenue.

One of the contenders to replace DRAM is memristor technology. Memristors aren’t new. UC Berkeley’s Professor Leon Chua predicted the existence of the memristor as a complementary circuit element to the resistor, capacitor, and inductor back in 1971. HP Labs fabricated the first working memristor back in 2008, which is when I wrote my first memristor article. Unlike Chua’s hypothetical device, which linked magnetic flux and charge, HP’s memristor altered its resistance depending on the history of the current passing through it. The current caused atomic-level restructuring within a titanium-dioxide storage layer, giving the memristor cell memory. The process was reversible, so the memristor’s resistance could be varied by passing an electrical current through it one way and then the other.

Despite achieving an initial storage density of 100 Gbits/cm2, HP appears to have abandoned further memristor development for bulk memory storage around 2015, although HP Labs researchers continue to report memristor-based developments such as a memristor-based laser that remembers its programmed emission wavelength, disclosed in 2020, and a memristor-based CAM (content addressable memory), disclosed in 2021.

Another company, 4DS, started memristor development a year before HP first announced its memristor development in 2008. The company has focused on a Perovskite material called PCMO (praseodymium, calcium, magnesium, oxygen) and uses this material to create area-based resistive RAM (ReRAM) cells. 4DS does not plan to make commercial chips based on this technology. Instead, it is developing memristor-based ReRAM as a licensable process technology that’s compatible with advanced CMOS manufacturing processes.

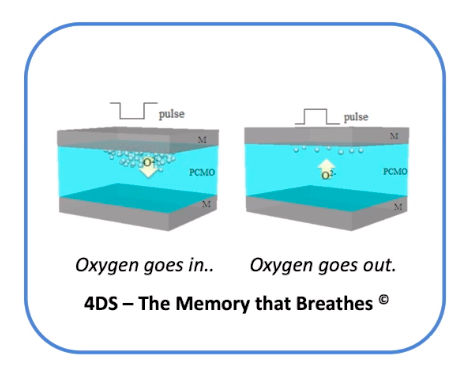

While most memristor research has focused on technologies that change cell resistivity by forming and breaking conductive filaments within the memristor cell’s storage layer, the 4DS area-based memristor changes its conductivity by using an electric field to drive oxygen atoms out of the PCMO layer, creating oxygen vacancies in the material, and putting the PMCO layer into its higher-resistance state. A reversed electric field drives the oxygen atoms back into the PMCO layer, putting the PMCO layer into its lower-resistance state, as shown below.

The 4DS memristor cell changes conductivity by either driving oxygen atoms out of the PCMO layer using a programming pulse of one polarity, or back into the PCMO layer using a pulse of the opposite polarity. Image credit: 4DS

4DS announced a memristor cell based on 40nm design rules and a working relationship with Western Digital subsidiary HGST back in 2016. Then the company went dark, until recently. There appears to have been some problems with the original technology. In 2017, 4DS started development of an improved cell technology with IMEC, the Belgian nanotechnology and semiconductor research organization. Now, 4DS claims to have developed a working megabit ReRAM test chip based on PCMO memristor cells drawn with 60nm design rules and plans to have a working device based on 20nm design rules fabricated at IMEC by the end of the year. This 20nm device will also have a 1Mbit capacity, but will demonstrate a cell density that could be used to fabricate a 1.6Gbit ReRAM chip.

The 4DS memristor cell exhibits some favorable memory characteristics. The cell’s write time is a fast 4.7 nsec, which is comparable to DRAM speeds. Demonstrated endurance for the cell is 109 write cycles, which far exceeds NAND Flash memory endurance by orders of magnitude. The scaled 20nm cells approach the density of DRAM cells, which are stuck around 10nm design rules. DRAM density continues to lag far behind EPROM cell densities, especially considering that 3D NAND Flash EPROMs now are built using more than two hundred layers. Kioxia recently announced that it plans to manufacture 1000-layer 3D NAND Flash EPROMs by 2031.

One characteristic where the 4DS area-based memristor cell differs from the filament-based memristor cells is persistence. Filament-based memristor cells are non-volatile. Essentially, they are infinitely persistent. The 4DS area-based memory cell is variably persistent, with data-retention times ranging from hours to months. Retention time depends on the length and strength of the programming pulse. A longer, stronger pulse drives out more oxygen atoms from deeper within the PCMO layer, extending the retention time. Consequently, it’s possible to electrically partition a memory device based on these 4DS memristor cells into longer- and shorter-duration persistence blocks, allowing a dynamic tradeoff between retention time and programming speed.

One additional memristor characteristic, yet to be fully explored, is the direct storage of analog values in the 4DS memristor cell using variable-length, variable-strength programming pulses. If this ability proves reliable and repeatable, it might be possible to store the neural network weights directly as analog quantities, which would greatly improve the storage density of the 4DS memristor cell in neural network applications and make the technology very attractive as on-chip memory for AI chip design. However, 4DS has not yet characterized this attribute of its memristor cells, so we’ll need to wait and see if this is a viable application for the 4DS memristor technology.

With Intel’s termination of phase-change-based Optane Persistent Memory in 2022 (see “Optane, We Hardly Knew Yeh”), the industry continues its quest to find memory technologies that are better than DRAM and NAND Flash EPROM (see “Can Any Emerging Memory Technology Topple DRAM and NAND Flash?”). Candidates have included ferroelectric RAM (FRAM), phase-change memory (PCM), magnetic RAM (MRAM), and memristor-based ReRAM. So far, all these DRAM and EPROM challengers produce working semiconductor memories, but they all suffer from one drawback or another. FRAM and MRAM suffer from a lack of memory density. PCM cannot tolerate elevated temperatures, which tend to anneal the bits right out of the memory cells. To date, memristor-based ReRAM has not been sufficiently developed to be seriously considered as a competitor. 4DS plans to change that situation.

HP’s original audio oscillator of 1938 used an incandescent light bulb as a short-term memristor: The lamp’s resistance increases with increasing filament temperature, which depends upon recent power dissipation. The lamp responds to the RMS oscillation level without distorting the sinewave: Higher level increases lamp resistance, thus reducing level.