In 1973, the Miller Brewing Company launched the “lite” beer revolution with an ad campaign that proclaimed “Tastes great. Less filling.” The company’s ads backed up the slogan by showing very masculine athletes including Ray Nitschke, Ben Davidson, Bubba Smith, and John Madden drinking (or at least holding) glasses of the lite beer, to make it look more manly. Going back a bit earlier, the Peter Paul Candy Company used a musical jingle that starts with the line, “Sometimes you feel like a nut, sometimes you don’t,” to define the key difference between its Mounds and Almond Joy candy bars. As the jingle continued, “Almond Joy’s got nuts. Mounds don’t.” Even earlier, the American Chicle Company advertised Certs mints as both a breath mint and a candy mint with the slogan, “Two mints in one!” These three consumer ad campaigns highlight products that satisfy differing customer needs. In that same vein, ST Microelectronics recently introduced a three-member family of SPI-interfaced serial EEPROMs that offer byte- and page-mode memory access, combining two of the defining aspects of EEPROMs and Flash memory in one device. This sort of dual-role non-volatile semiconductor memory is likely to reduce design effort and parts count by eliminating the need to have separate EEPROMs to hold code and data in smaller embedded designs.

In the beginning, there was only EPROM. Actually, in the beginning there was nothing but magnetic core memory, which provided both random access and non-volatile memory storage, but, in November 1971, Intel introduced the world’s first commercial EPROM, the 1702, alongside the world’s first commercial microprocessor, the 4004. (Intel first demonstrated its EPROM technology at the 1971 International Solid State Circuits Conference in February and then introduced the commercial product, the 1702, in November.) Following the 1702’s introduction, EPROMs quickly became essential to the development of microprocessor-based embedded systems because they could hold code and static data in systems that could not afford the cost, physical volume, or power consumption of mass storage devices.

IBM patented an electrically reprogrammable non-volatile semiconductor memory based on Fowler-Nordheim tunneling the following year, and modern EEPROMs from several semiconductor vendors started appearing in the latter half of the 1970s. These early EEPROMs offered only byte (or word) access. In an effort to reduce EEPROM chip size, Toshiba’s Fujio Masuoka developed block- or page-accessible Flash EEPROM (now just called Flash memory) at Toshiba in 1980. It took Toshiba seven years to bring these devices to market, but that’s a different story.

Flash memory cells are smaller than EEPROM cells because each Flash memory cell does not need a separate erase transistor for each memory location. Flash memory is therefore denser and it costs less per bit. The embedded design community quickly adopted Flash memory for code storage as software storage ballooned in all systems. Meanwhile, the byte addressability of EEPROM has kept it popular for volatile data storage in embedded designs. Today, many embedded systems have required at least one EEPROM for data storage and one Flash memory IC for code storage.

ST’s newest EEPROM family provides byte-level and page-level non-volatile memory access in one device. There are three members in the family – the M95P08, M95P16, and M95P32 – with storage capacities of 8, 16, and 32 Mbits respectively. Each device is available in an SO-8 SOIC package or in a wafer level chip scale (WLCS) BGA package. The three SO-8 packages are pin-compatible, so you can design one footprint on your circuit board that will accommodate any of the three devices. Owing to the different chip sizes, M95P devices in the smaller WLCS packages do not appear to have compatible footprints, as shown below.

ST’s three members of the M95P serial EEPROM family are offered in standard, pin-compatible SO-8 packages and in three different wafer level chip scale (WLCS) packages.

All three M95P serial EEPROM members offer byte-level read/write access and accept page/block/sector/chip erase commands. All four devices support single/dual/quad (1-, 2-, and 4-bit) data transfers over the SPI bus. The 8Mbit M95P08 memory array is divided into 2048 erasable pages of 512 bytes and can be accessed as 256 erasable sectors of 4 Kbytes, 16 erasable blocks of 64 Kbytes, or as an entirely erasable array. The 16Mbit M95P16 memory array is divided into 4096 erasable pages of 512 bytes and can be accessed as 512 erasable sectors of 4 Kbytes, 32 erasable blocks of 64 Kbytes, or as an entirely erasable array. The 32Mbit M95P16 memory array is divided into 8192 erasable pages of 512 bytes and can be accessed as 1024 erasable sectors of 4 Kbytes, 64 erasable blocks of 64 Kbytes, or as an entirely erasable array.

All three EEPROM devices offer two additional non-volatile memory pages that can be used for identification purposes. The first of these two memory pages contains the device ID, device size, and a user-defined data byte. The second of these memory pages can be used to store sensitive application parameters that can be permanently locked in read-only mode.

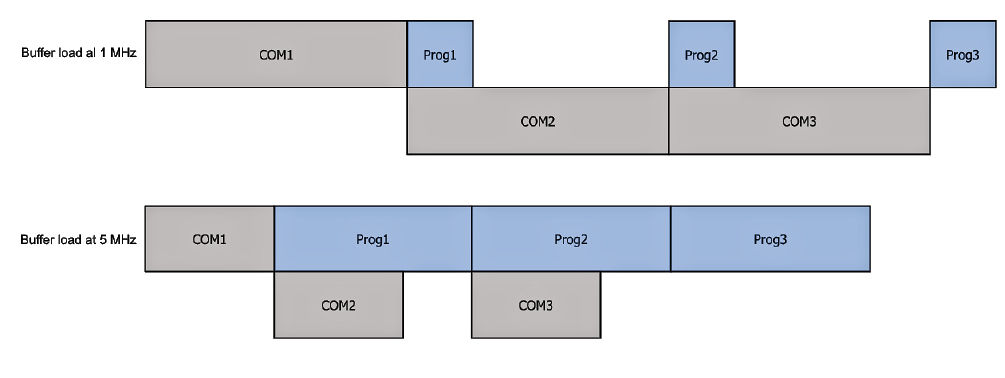

The Page EEPROM’s page-mode accessibility provides faster memory access for large memory reads and writes. A 512-byte buffer in each device stores data to be programmed, which allows data transfers to overlap page storage cycles. The maximum SPI clock rate for these devices is 80 MHz, but reads are limited to 50 MHz. The amount of overlap depends on the clock frequency used for the SPI connection between the host device and the serial EEPROM, as shown below.

Depending on the SPI port’s clock rate, the ST M95P serial EEPROMs can fully overlap data transfers with page storage. At 1 MHz, data transfer takes longer than page programming. At 5 MHz, the two processes completely overlap. The maximum SPI clock rate for these serial EEPROMs is 80 MHz. When the SPI clock frequency is 80 MHz, communication over the SPI bus takes 4% of the total time. Image credit: ST Microelectronics

The host device must send a Write Enable (WREN) instruction to an M95P Page EEPROM before performing a page write. Then the host sends a Write instruction followed by the data. The full sequence with timing (based on a 12.5 MHz SPI clock) looks like this:

• WREN instruction: 0.64 μs at 12.5 MHz

• Page program instruction: 330 μs at 12.5 MHz

• Writing one page (512 bytes) with memory array programming: 1200 μs

Pages must be erased by a separate command before they can be written. The M95P Page EEPROM’s page erases and memory accesses are controlled by a read/write/erase controller internal to the chip. The host can poll the Page EEPROM to find out when the current programming completes. If there’s another page to be written to the EEPROM, the host must wait until the current programming cycle completes.

According to ST, the M95P08, M95P16, and M95P32 Page EEPROMs are in production now. Volume pricing starts at $0.50 for the 8Mbit M95P08. ST also offers the X-NUCLEO-PGEEZ1 expansion board, which incorporates one of the M95P Page EEPROMs, designed for the company’s STM32 Nucleo microcontroller development boards and the X-CUBE-EEPROM A1 software package so that developers can learn how to interact with the M95P Page EEPROMs and adopt them to new application designs. Although these new serial Page EEPROMs are not as large as the largest serial Flash memories on the market today, they are likely to find use in many embedded designs that may not require all the capacity of larger devices.