This is a follow-on to my previous column, All Change! As you may recall, assuming you are a regular muller of my meandering musings, that column described the presentation I gave earlier this week to the MSc students studying Embedded Computing at the Norwegian University of Science and Technology (NTNU) in Trondheim, Norway.

Possibly in order to lure the unsuspecting and more gullible students to attend, this talk was billed as being part of the university’s “Distinguished Lecture Series.” My mother is going to be so proud. She will be able to “dine out” at her hairdresser’s for weeks on this, not least that she often tells the tortuous tale of when she and my dear old dad attended a parent-teacher evening at my high school, only to be told by more than one member of the faculty that I was a complete idiot who would never make anything of himself (I wondered why they looked so glum on their return).

Yesterday (assuming you are reading this on Thursday 8th September, which is when it’s scheduled to post on the EE Journal website), I gave my keynote presentation to the attendees at the FPGA Forum, which is the event “to see and be seen” for practitioners of the mystic FPGA arts, purveyors of FPGAs to the haut monde, and even muddling managers who are desperate for any nuggets of knowledge and tidbits of trivia that will make them appear to have a clue as to what’s going on in the world (bless their little cotton socks).

Just to make sure that we’re all tap-dancing to the same skirl of the bagpipes, I’m actually penning these words in the past from your perspective—just a few hours before boarding my flight to Norway, in fact—because I thought you might be interested to hear what I’m planning on talking about, but I won’t have any free time to do anything while I’m there apart from give my presentations and bask in adulation and applause (a boy can dream).

The last time I presented the keynote at the FPGA Forum was 2012, which was ten years ago at the time of this writing. Eeek! Where does the time go? In fact, I will start my talk by reminding everyone that 10 years have passed since my previous visit, and then I’ll ask who was there 10 years ago. If only a few people raise their hands, I’ll say, “Dang, I could have re-used my original presentation.” Alternatively, if I see a sea of hands, I can say, “Thank goodness I have a new presentation!” I know this isn’t high comedy, but it will provide a nice way to get the ball rolling.

Next, I’m going to point out that 10 years isn’t much time in the scheme of things and that initially I was worried that I wouldn’t have anything new to talk about. But then I thought about all of the flavors of reality that were the stuff of dreams 10 short years ago, like augmented reality (AR) and virtual reality (VR). “Also,” I’ll say, “we might find something to say about artificial intelligence (AI), along with robots that can run, jump, dance, and perform somersaults” (the best I can do myself these days is fall over).

Since this is the FPGA Forum, I’m going to note that, sad to relate, some of the FPGA companies we talked about 10 years ago are no longer with us. For example, Tier Logic had an interesting technology in which they implemented the configuration RAM in the upper metallization layers to form their SRAM-based 3D TierFPGAs. To lower price and power consumption for mass-production, they could generate a new version of the device where the configuration RAM cells were replaced with hardwired equivalents, resulting in TierASICs with the same timing as the FPGAs.

Another very interesting company was Tabular, which was ranked third on the Wall Street Journal’s annual “Next Big Thing” list in 2012. Tabular’s SpaceTime architecture allowed a 200 MHz external user clock to act as a 1.6 GHz internal SpaceTime clock. From cycle-to-cycle, the data stayed where it was while the configuration changed around it. The result was smaller dies with easier to close timing. Towards the end they introduced incredible test capabilities, including the ability to observe and control any node in the device on-the-fly while the chip was running. And then, just when things were getting exciting… they shut up shop (sad face).

Happily, we can also talk about some new companies that have joined the FPGA party, such as Rapid Silicon, which is a provider of AI-enabled application-specific FPGAs and which offers the world’s first commercial FPGA EDA environment based on end-to-end open-source software.

And then we have the folks at Efinix with their Quantum fabric, the basic building block of which is the eXchangeable Logic and Routing (XLR) cell. An XLR cell can function as either a LUT-based logic cell or a routing switch encoded with a scalable, flexible routing structure. The result of this software-configurable logic and routing and high-performance adaptive interconnect is a 4X improvement in terms of Power-Performance-Area (PPA) as compared to traditional SRAM-based FPGAs created at the same technology node.

I’ll also point out that when I was there last time, we talked about a company called Silego, whose claim to fame was a series of teeny-tiny mixed-signal programmable devices called GPAKs. Silego was acquired by Dialog Semiconductor, which was itself acquired by Renesas. Recently, Renesas announced a new line of devices called ForgeFPGAs, which are derived from the original Silego technology. Initial devices are pure digital with 1K and 2K LUTs but I wouldn’t be surprised to see mixed-signal stuff coming in the future. Price in volume is under $0.50 and the GUI-based design tool is free.

And, once again, since this is the FPGA Forum, I would be remiss if I didn’t briefly mention what all of the usual suspects (a.k.a. key players) have been getting up to. But we won’t spend too much time on this because we have other poisson à frire as the old saying goes.

There are, of course, a lot of companies who are doing all sorts of interesting things with FPGAs but—since we will be limited for time, and on the basis that I served my time creating test programs for PCBs—I’m just going to give a shout out to the folks at Testonica. Amongst the many other products and services that they offer, they have a tool called Quick Instruments. The idea is that a lot of today’s boards feature a large FPGA or SoC FPGA. The core of Quick Instruments is a library of pre-created embedded test instruments for standard memory, peripheral, and communications devices. When provided with a description of the system, including the type/family of FPGA—they support devices from Altera (Intel), Lattice Semiconductor, and Xilinx (AMD)—the types of external devices, pin maps, and register maps, Quick Instruments automatically generates and compiles the corresponding firmware test suite, which is loaded into the board’s FPGA or SoC FPGA (see Got FPGA? Got Test!).

One of the great things about being me—apart from my outrageous good looks and my trend-setting sense of style, of course—is that I’m introduced to a lot of awesome technologies as part of my writings. On this basis, I’m going to use the rest of my presentation to discuss a small selection of some of the interesting things to which I’ve been exposed, and also to talk about some of the technologies that could be heading our way in the not-so-distant future.

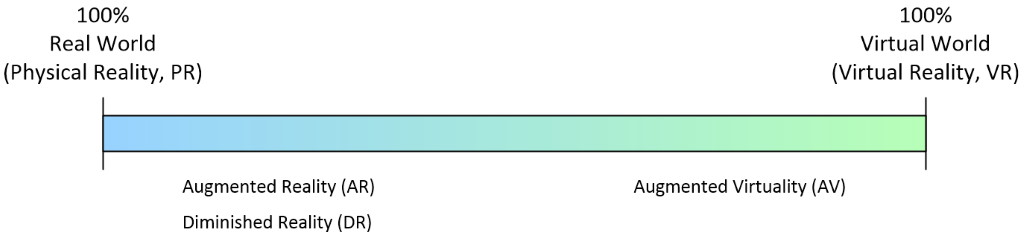

Just to set the scene, we’ll start by discussing the different flavors of reality. As I mentioned in The Metaverse is Coming and GridRaster Is Ready to Take Us There, at one end of the scale, we have the real world, which we might dub physical reality (PT). At the other end we have VR, where everything is we see and hear is computer-generated.

In addition to AR, we also have diminished reality (DR) in which information is removed from PT, augmented virtuality (VR) in which real objects and/or people are added into VR, and mixed reality (MR) that encompasses AR, DR, AV, and VR (don’t get me started talking about hyper reality (HR)).

One of the things that’s been holding us back is how we access these various realities. Traditional headsets have all sorts of problems, like weight, low-resolution, and restricted field of view. But there is hope of better things to come, like AR headsets that look like regular glasses with 8K x 6K resolution for each eye (see Kura’s AR Glasses are Meta-Droolworthy!). Another interesting company that entered the fray just a couple of months ago is Swave photonics, which is working on delivering lifelike, high-resolution, holographic 3D images that are “viewable with the naked eye, with no compromises” (see Did the Metaverse’s Holy Grail Just Arrive?).

I’m also going to talk about AI and related companies like Mythic, Aspinity, Algolux, and AI Storm. And I won’t be able to restrain myself from waffling about the latest and greatest robots from Halodi and the super-sensing robot skin from Bebop Sensors. As part of this, I’m going to hand out some Braille test cards so the attendees can see (no pun intended) how hard it is to detect Braille characters with your fingers, and then show a picture of a robot finger equipped with Bebop RoboSkin reading Braille.

Good grief! There’s so much more to talk about, but I fear I’m running out of time. I’ve still got to pack and then race down to the airport, so I’m afraid I will have to bid you adieu until I return in my next column. Until then, as always, I welcome your comments (especially the nice ones) and questions (especially the easy ones).