Porsche is a driver’s car – a performance car… but it’s got no cup holders.” – Jason McCoy

You want the 140-character version? MIPS has a new processor with parity.

You want the longer, more detailed version? Uh… MIPS has a new processor with parity… and some ECC. And some additional technical documentation to help with safety certification. But the CPU itself? Pretty much the same one as before.

That’s not to belittle the new I6500-F. I’m sure it was a lot of work, and it’s nice to see the engineers at Imagination Technologies gainfully employed. It’s just that the improvements to the -F version over its non-F predecessor are, shall we say, narrowly focused.

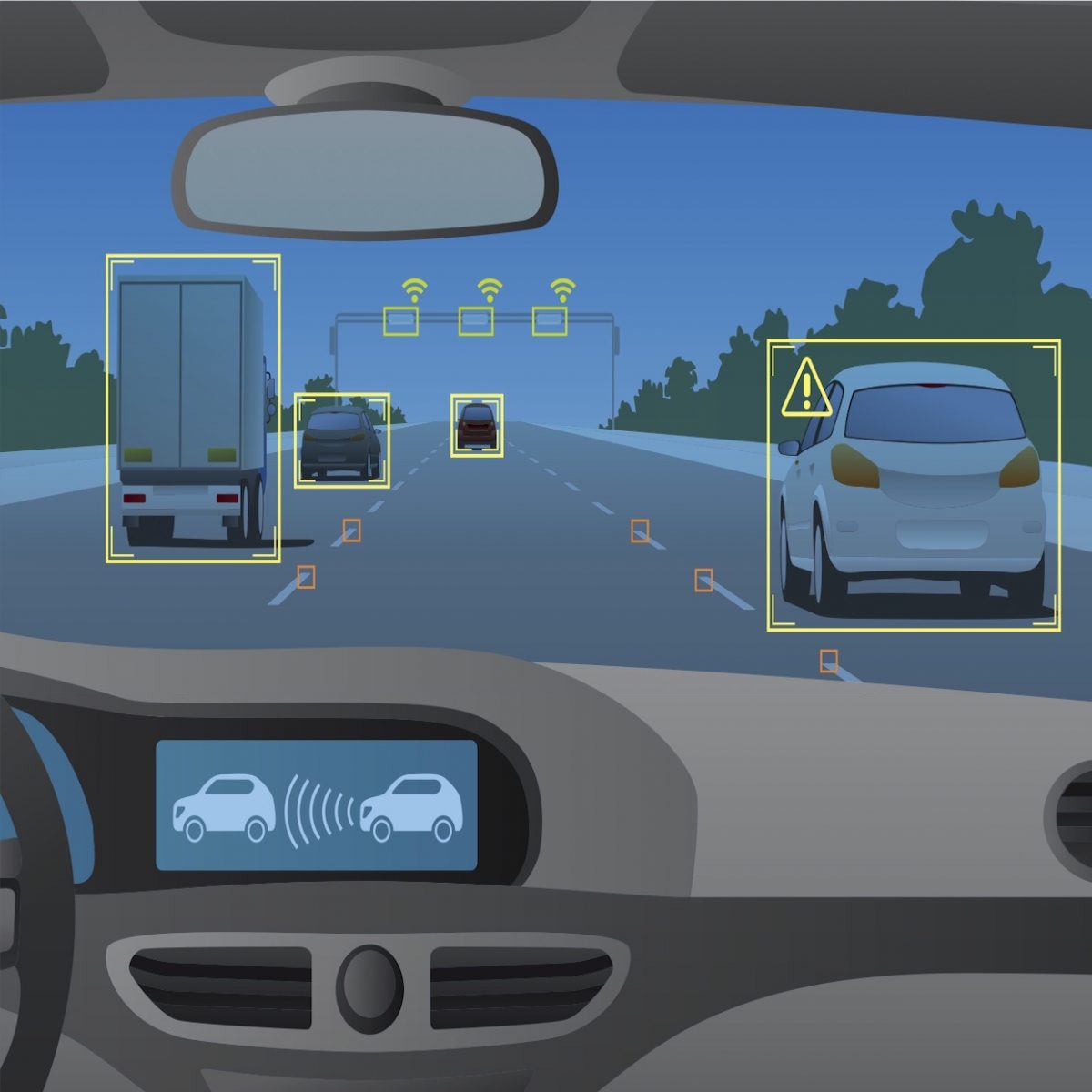

Imagination pitches the new I6500-F as the ideal processor for safety-critical applications, and that might very well be true. Our discussion included a lot of talk about autonomous vehicles, ASIL standards, industrial robotics, and AI (artificial intelligence). At first blush, you’d think the company had invented an entirely new processor architecture dedicated to machine intelligence. Instead, it’s tweaked one of its existing processors to make it easier to test and document thoroughly – something that safety inspectors really like.

Imagination Technologies obviously doesn’t build autonomous vehicles. Its customers don’t build cars, either, and even its customers’ customers probably don’t build cars. But they are all part of the long chain of technology that ultimately will (or may) wind up in cars and other safety-critical systems. That means Imagination – if it’s smart – will do everything it can to make its little link in the chain compatible with the standards and expectations of the greater certification process.

That’s a tricky thing for an IP company to do. After all, they don’t really make anything. How do you certify intangible IP? The answer is, you don’t. But you can make it easier for your customer (or your customer’s customer, ad infinitum) to achieve certification. Or at the very least, you don’t place any roadblocks in the path of that certification. You help where you can, and where you can’t help, you get out of the way.

In the certification world, that’s known as “safety element out of context” (SEooC). That is, it’s not really a testable element by itself; it’s a piece of something that eventually will be tested. For automotive applications, that includes adherence to the ISO 26262 standard and the automotive safety integrity levels (ASIL) A through D. The I6500-F does not, by itself, comply with any of these standards, but it lays the groundwork for eventual certification, hopefully to ASIL-D, the highest level. The process is a bit like the ISO 9001 hoops we all jumped through about 20 years ago.

The original MIPS I6500, you’ll recall, was released into the wild late last year, and was itself based on the two-year-old I6400 processor core. The big headline feature of the I6500 over the previous I6400 was multiprocessing. The I6500 had the interfaces and cache architecture to work well in mixed clusters, paving the way for massive thousand-CPU superchips, if that’s what you wanted. (It also, not incidentally, allowed MIPS processors to work alongside ARM processors. These guys are nothing if not practical.)

The new I6500-F has all of that, plus internal checking mechanisms that enable internal diagnostics, self-tests, scans, and verification that the normal I6500 couldn’t do. The internal on-core buses now have parity, the internal cache RAM has ECC, and the CPU cores have internal logic BIST (built-in self-test).

None of this makes the I6500-F run any faster – it’s a wee bit slower than the standard I6500, in fact – but they do go a long way toward making its eventual safety certification more doable.

The reliability and testability features of the I6500-F aren’t just a one-off. They’re the start of a new subcategory of processors that Imagination Technologies is dubbing “FortifAI” (everybody groan now). That means we can expect -F variations of other MIPS processors over time as the company retroactively tweaks some of its existing cores to add these features. They’ll also likely appear on almost all new CPU cores going forward. Clearly, Imagination is pinning a lot of hope on the safety-critical market and the demands it will place on silicon vendors.

Is the I6500-F the first safety-focused processor IP? Nope, not even close. Synopsys rolled out its own ASIL-D processor IP just a few months ago, and ARM has done something vaguely similar. Actual chip companies, like Renesas and TI, have also produced ASIL-compatible microcontrollers. It’s a booming business making chips that don’t fail. Or more accurately, that fail in precisely documented ways.

Maybe autonomous vehicles and other safety-critical applications will become The Next Big Thing for MIPS. Let’s hope so. It’s no secret that Imagination Technologies is in a world of hurt right now, and the company could use a hit product to reverse its fortunes. Self-driving pioneer Mobileye favors MIPS processors because of their multithreading ability, and the company almost certainly had some input into the I6500-F’s development. If Mobileye (soon to become part of Intel) becomes a successful provider of autonomous technology, the MIPS architecture could go along for the ride. MIPS might be a huge deal in a few years. Stranger things have happened. Apple exhumed itself with the first iPod. Maybe MIPS can make a comeback with cars. There’s a lot riding on the outcome.