Literally the day after writing the article about the Microchip PolarFire SoC Discovery Kit based on the company’s PolarFire SoC FPGA, Microchip gave me a preview of two closely related products. The new products, announced last month, are the company’s PIC64GX microcontroller and a development board for this microcontroller called the PIC64GX Curiosity Kit. The PolarFire SoC Discovery Kit discussed in my previous article is based on Microchip’s PolarFire SoC FPGA, which melds the software programmability of five 64-bit RISC-V processors with a fair-sized chunk of FPGA fabric. (See “Microchip’s PolarFire SoC Discovery Kit provides low-cost access to a powerful SoC FPGA development platform.”) To put it as succinctly as possible, the PIC64GX is a microcontroller based on the PolarFire SoC FPGA’s RISC-V microprocessor subsystem with a DDR4/LPDDR4 SDRAM controller and some additional hardened peripherals, but minus the FPGA fabric. The PolarFire SoC FPGA and the PIC64GX microcontroller are pin- and software-compatible, which means you can start developing a product using the PIC64GX microcontroller, and then, if you need extra processing horsepower, switch to the PolarFire SoC FPGA.

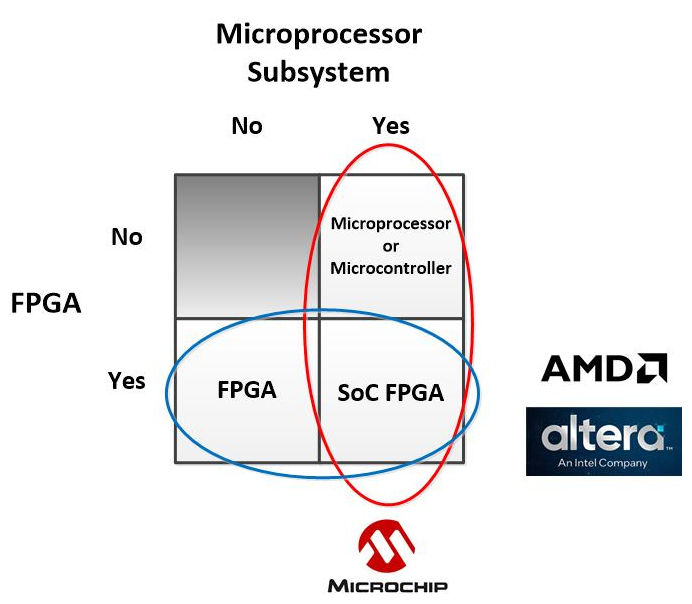

I think this announcement represents a well-thought-out approach to product extension on Microchip’s part, and it reflects some very different thinking from the FPGA offerings from AMD and Altera. Those two vendors offer pin-compatible FPGAs with and without microprocessor subsystems. Microchip is offering a quint-core, 64-bit RISC-V microcontroller that’s pin and software compatible with its PolarFire SoC FPGA, but with the deletion of the SoC FPGA’s FPGA fabric. A Venn diagram of these product concepts looks like this:

A Venn Diagram showing AMD’s, Altera’s, and Microchip’s approaches to compatible FPGAs, SoC FPGAs, and Microcontrollers. Image credit: Steve Leibson

Of course, Microchip is happy to sell PolarFire FPGAs (with no processor cores) to you, but those FPGAs do not look exactly like the FPGA fabric arrays in the PolarFire SoC FPGAs because they’re not offered with an equivalent number of resources, so they’re not really applicable to the Venn diagram shown above.

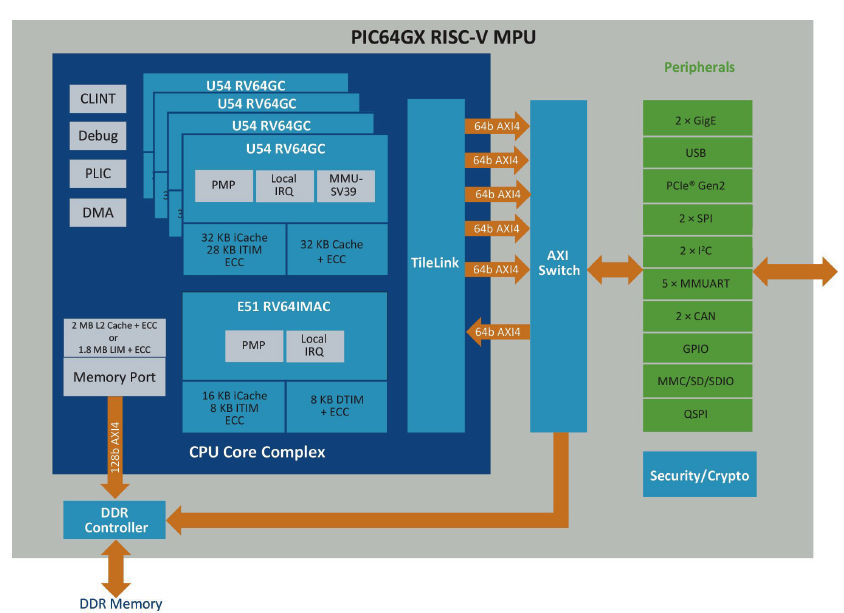

Because the PIC64GX consists solely of processor cores and has no FPGA fabric, Microchip’s presentation for the device provided much more detail about the five 64-bit RISC-V processors in the package. The 5-processor subsystem in the PolarFire SoC FPGA is the same one used for creating the PIC64GX microcontroller, so the details provided about the PIC64GX microcontroller apply to the microprocessor subsystem in the PolarFire SoC FPGA as well. Microchip has drawn a new diagram of this microprocessor subsystem for the PIC64GX, and I think it’s more illustrative of the block. Here it is:

Block diagram of the Microchip PIC64GX microcontroller showing the five 64-bit RISC-V microprocessor cores and the additional peripheral circuitry. Image credit: Microchip

One of the PIC64GX’s five 64-bit RISC-V cores is an RV64IMAC. The “E51” designation tells us that this is a SiFive RISC-V IP core. This processor core has a 16Kbyte L1 instruction cache and a tightly integrated 8Kbyte data RAM instead of an L1 data cache. This processor core runs bare-metal code called “Hart Software Services” that functions as a zero-stage boot loader for the rest of the chip. This core’s primary responsibility is to provide boot and housekeeping services for the rest of the microcontroller. However, this is a 64-bit processor core, which represents more processing horsepower than many processors used on other microcontrollers. This processor core has full access to all on-chip peripherals and the SDRAM controller, and it is fully user-programmable, so it’s possible to run real-time, user-generated application code on this processor in addition to the other four cores.

The other four processor cores are RISC-V RV64IMAFDC application cores with separate 32Kbyte instruction and data caches. Their “U54” designation indicates that these are also SiFive RISC-V processor cores. Each of the PIC64GX microcontroller’s RISC-V application cores can run Linux, some other RTOS, or bare-metal code. Maximum clock speed for all five processor cores is 625 MHz. Unlike the PolarFire SoC FPGA, there’s no -1 version of the PIC64GX microcontroller, so there’s no option for the PIC64GX microcontroller to match the PolarFire SoC FPGA’s 667MHz maximum clock speed.

Like the PolarFire SoC FPGA, the PIC64GX microcontroller integrates a 2Mbyte L2 cache that’s shared by its four RISC-V application cores. When operating as a 4-core symmetric multiprocessing system running Linux or some other multiprocessor-capable operating system, the four application processor cores share the L2 cache. However, it’s possible to configure the L2 cache as a local memory for one or more of the application cores running in asymmetric mode to accommodate code that needs to run in real time with deterministic timing. The 2Mbyte L2 cache can be configured with 128Kbyte granularity, as illustrated in the example below.

The PIC64GX micrcontroller’s application cores can be configured for Symmetric Multiprocessor (SMP) or can be individually configured as independent processors running an RTOS or bare-metal code with private and shared coherent buffer memory carved out of the L2 cache. Image credit: Microchip

The PIC64GX microcontroller also shares the security/cryptography block with the PolarFire SoC FPGA. This block contains cryptographic hardware accelerators that speed 256-bit AES and SHA calculations. The security/crypto block also incorporates anti-tamper features and a true random number generator. Because the RISC-V processor cores in the PIC64GX microcontroller execute instructions in order, they’re not susceptible to side-channel exploits such as Spectre and Meltdown, which further increases the security of code running on these devices. All on-chip memories have ECC with SECDED (single error correction, double error detection).

As with the PolarFire SoC FPGA, Microchip is offering a low-cost development board for the GX1000 version of the PIC64GX microcontroller. It’s called the PIC64GX Curiosity Kit, which the company has integrated into its MPLAB Extensions for Microsoft’s Visual Studio (VS) Code software development environment.

The initial release of the PIC64GX microcontroller is for the GX1000 version of the device. Microchip also announced that it is preparing a GX1100 version, to be available in about a year, with additional hardened functional blocks that will include a multiprotocol video encoder and a Machine Learning hardware accelerator.

Coincident with the PIC64GX microcontroller announcement, Microchip also announced a very different PIC64 variant, also based on the RISC-V ISA: the PIC64 High-Performance Spaceflight Computing (PIC64-HPSC) microprocessor. This device is the result of a collaboration involving Microchip, NASA, and SiFive (see “NASA Recruits Microchip, SiFive, and RISC-V to Develop 12-Core Processor SoC for Autonomous Space Missions”), and Microchip has now rolled this device into its new PIC64 family. The HPSC concept as originally developed by NASA was based on eight Arm Cortex-A53 microprocessor cores, but the final device as developed by Microchip and SiFive is now based on one S7 and eight X280 64-bit RISC-V CPU cores from SiFive. The PIC64-HPSC also extends Time Sensitive Networking (TSN) into space with an integrated 240Gbps Ethernet switch supporting 10 GbE connectivity.

A radiation-tolerant version of this device, the PIC64-HPSC RT, can meet the needs of satellites and satellite constellations in low earth orbit (LEO) such as communications and navigation satellites. A radiation-hardened version, the PIC64-HPSC RH provides the local processing power needed to execute complex real-time tasks, such as autonomous rover hazard avoidance on the Moon’s surface, and for long-duration, deep-space missions to Mars, to other planets in the Solar System, to the asteroid belt, and beyond. Microchip says that PIC64-HPSC samples will be available to the company’s early access partners early in 2025.