Note: On October 3, Intel announced plans to transform its FPGA group into an independent operating company starting January 1, 2024. See “Intel plans to spin off FPGA group as an independent company nine years after buying Altera.”

Last month, just before Intel FPGA Technology Day (IFTD) 2023, the company made several announcements regarding its flagship Agilex FPGA families. The announcement reminded me of an old English rhyme about the things a bride needs: something old, something new, something borrowed, and, of course, since we’re talking about Intel here, something blue.

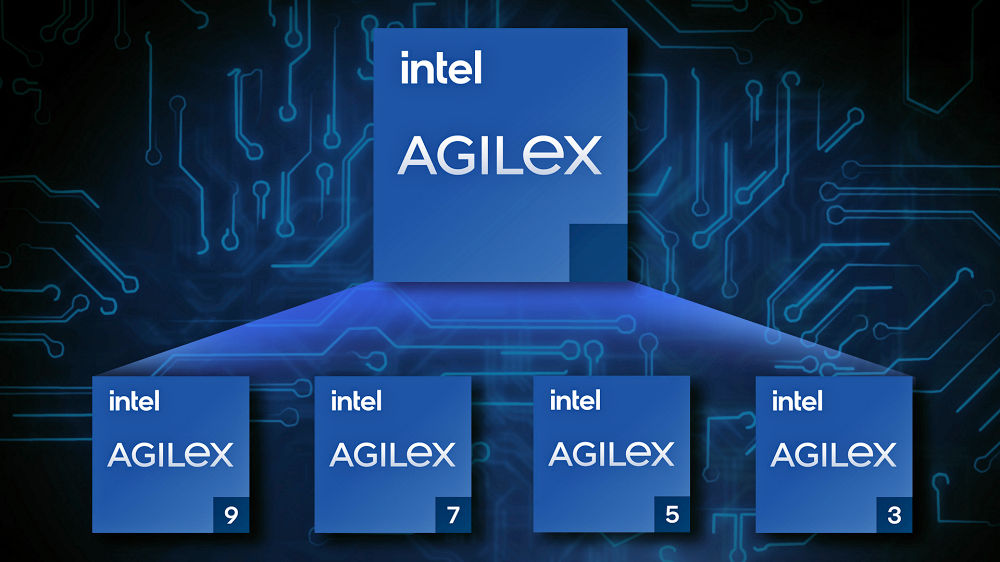

Intel has added the Intel Agilex 5 and 3 mid-range and low-end FPGA families to its growing line of Agilex FPGAs. Image credit: Intel

Something New

Intel has decided that “Agilex” will be the company’s FPGA brand going forward. To that end, the company announced the low-end (or “cost optimized” in FPGA speak) Agilex 3 FPGAs, which are power and cost-optimized FPGAs stuffed into compact form factors for designs that have need for the FPGAs to consume minimal pc board real estate. Intel is positioning Agilex 3 devices as “essential building blocks targeted for a range of applications across markets, including system/board monitoring and management, video and vision, protocol expansion, portable imaging and displays, sensor fusion, drives, robotics I/O expansion and others.”

The Agilex 3 family includes B- and C-Series devices. Agilex 3 B-Series FPGAs have higher I/O density and are housed in packages with smaller footprints. They also consume less power than Intel MAX® 10 FPGAs. Agilex 3 B-Series FPGAs target board- and system-level management functions, including Intel’s server platform management (PFM) applications.

Intel has long ignored the low end of the FPGA market, as has AMD, which has allowed Lattice Semiconductor to make significant market gains in that arena. Both Intel and AMD have recently re-energized their low-end aspirations for the programmable-logic market, and the Intel Agilex 3 family is clearly a move designed to stop or even reverse Lattice’s gains. Lest you think that Intel is ready to obsolete its existing low-end devices, the Cyclone and MAX FPGAs and CPLDs, the company has already announced that it has made the strategic investments needed to ensure that these older products will continue to be available at least until the year 2035. Of course, the price for these older components is not guaranteed, so caveat emptor. For new low-end FPGA designs, you might consider using the new Intel Agilex 3 FPGAs.

Something Old

A couple of the IFTD 2023 announcements discussed older things:

Intel Agilex 7 I-Series FPGAs with R-Tile are now shipping CXL IP with 2.0 features in volume: Intel announced that it was shipping “production-qualified” Agilex 7 family devices with R-tiles (tiles are Intel-speak for chiplets) on May 22, 2023. Intel uses chiplets in the Agilex 7 FPGA family to provide new I/O and integrated memory capabilities. The R-tile adds hardware support for PCIe Gen5 and CXL 1.1 and certain CXL 2.0 features as well. The CXL capabilities of these Agilex 7 I-Series FPGAs match those of the upcoming Intel Sierra Forrest and Granite Rapids Xeon CPUs, which are scheduled for delivery next year. Sierra Forrest Xeon CPUs are based on the company’s E-core x86 processors (“E” stands for “efficiency,” so you get more E cores with less performance per core) and Granite Rapids CPUs are based on P-core processors (“P” stands for “performance,” so you get more powerful processor cores but fewer of them). Intel Early Access Program (EAP) software customers will be able to access the CXL features of the Agilex 7 FPGAs with R-tiles in the version 23.4 release of Intel Quartus Prime Design Software.

Intel Agilex 5 FPGAs also fall into the “something old” category. Last year, at IFTD 2022, Intel announced the mid-tier Intel Agilex 5 D-series FPGAs and SoCs and previewed the Intel Agilex 5 E-series, formerly known as “Sundance Mesa.” The company provided a little more information about the Agilex 5 E-series FPGAs at this year’s IFTD. These devices emphasize cost-effectiveness and lower power consumption with commensurate performance for embedded edge applications. (See “Intel Introduces Two Monolithic Agilex FPGA and SoC Families, Part 1” and “Intel Introduces Two Monolithic Agilex FPGA and SoC Families, Part 2.”

Currently, Intel is working with multiple customers to design Agilex 5 E-Series FPGAs into systems as part of its early access program. The company plans to begin sampling these FPGAs to early access customers in the fourth quarter of 2023 and will begin broad market shipments of engineering samples to customers in the first quarter of 2024.

Something Borrowed

Intel Agilex 5 D- and E-series FPGA SoCs incorporate the AI tensor block taken (or borrowed) from the company’s Stratix 10 NX FPGA, announced in mid-2020. The AI tensor block in the Stratix 10 NX FPGA contains 30 multipliers and 30 accumulators instead of the two multipliers and two accumulators in the DSP block usually found in the Agilex second-generation Hyperflex FPGA fabric. The AI tensor block’s multipliers are smaller than multipliers used in an FPGA DSP block and are designed to handle lower precision numerical formats including INT4, INT8, Block Floating Point 12, and Block Floating Point 16, which are data types used for AI inferencing workloads. Intel originally partnered with Microsoft to develop the AI Tensor block for the Stratix 10 NX FPGA, specifically to help Microsoft accelerate AI workloads in the data center, but AI inferencing workloads have now extended well into edge applications, which is where the Intel Agilex 5 FPGAs will likely find the most use.

The Agilex 5 D- and E-series SoCs also incorporate something new: a Hard Processor System (HPS) that consists of a dual-core Arm Cortex-A76 and a dual-core Arm Cortex-A55 processor integrated with a system memory management unit. This HPS represents an upgrade from the HPS incorporated into previous Agilex SoCs. Intel has been providing the Simics Simulator to software developers for code creation for several years now, and the company recently announced that it was supporting RISC-V software development with this simulator. The latest version of this simulator now supports the new Intel Agilex 5 HPS. Intel claims that the availability of the Simics simulator, months before the Agilex 5 SoC silicon is available, allows software-development teams to accelerate product development by an estimated six to nine months.

Note: The original version of the Simics simulator is more than three decades old, so it certainly qualifies as something old. Simics was a commercial product for 25 years and has been available in a public release since 2021, so it’s also something borrowed, with permission. (See “The Public Release of Intel Simics (and More)” and “Introducing RISC-V in the Simics Simulator.”)

You might also consider the RISC-V ISA to be something borrowed, and Intel has offered NIOS V soft-core processors specifically tailored to Intel FPGAs for a while now. The company has added a new NIOS V core to its existing two NIOS processor cores based on the RISC-V ISA. The newly introduced NIOS V/c (“c” is for “compact”) processor is based on the RISC-V RV32I Instruction Set Architecture (ISA) and joins the company’s existing NIOS V/m and NIOS V/g soft-core processors, which are based on the RISC-V RV32AI and RV32IMA ISAs respectively. Intel says that it developed the NIOS V/c soft-core processor based on the RISC-V ISA as a drop-in hardware replacement for the existing NIOS II/e processor core, which was based on a proprietary ISA. Both the NIOS V/c and NIOS II/e processor cores were designed for minimum core size and let the performance fall where it may. All three NIOS V soft cores are supported by a large and growing RISC-V ecosystem with 3rd-party software vendors including Micrium, Ashling, and others.

Something Big Blue

Intel is now providing FPGA developers with full, open-source access to the Open FPGA Stack (OFS) hardware code, software code, and technical documentation. OFS consists of a hardware and software infrastructure comprised of composable hardware code and kernel code. Intel, often called “Big Blue” because of the corporate color scheme, developed OFS to make it easier for developers to use FPGAs for their designs. OFS currently supports Intel Agilex and Stratix 10 FPGAs, and several partners including BittWare, Hitek Systems, and SigmaX now offer platforms and applications based on OFS.

Individually, none of these IFTD-related announcements will shake the FPGA world to its core. Taken together, these announcements demonstrate that Intel remains committed to the relatively small FPGA arena, even while Big Blue’s Xeon and Core CPUs and SoCs are the locomotives that continue to power the corporate train from a revenue perspective.

Heh, Big Blue used to be IBM; how times have changed!