Arrow has just launched a development board for Intel’s soon-to-be-produced Agilex 5 SoC FPGAs, and two more such boards wait in the wings. The Arrow AXE5-Eagle board sports one Intel Agilex 5 E-series SoC FPGA. Initially, these development boards will incorporate an engineering sample of the SoC FPGA with 656K logic elements (LEs), while production boards, available by the end of the first half of 2024, will incorporate Agilex 5 devices with 334K LEs. The target price for the board is $995, which is subject to change, according to Arrow. Intel formally announced the Agilex 5 D- and E-series SoC FPGA families in January (see “Intel Introduces Two Monolithic Agilex FPGA and SoC Families, Part 2: Sundance Mesa is now the Agilex 5 E-Series”). The company has just gotten the first Agilex 5 SoC FPGA engineering samples back from the fab and expects to be shipping parts to customers by Q1 of 2024.

The Intel Agilex 5 devices are the first mid-range SoC FPGAs and FPGAs in the Agilex family, which started out as Intel’s high-end FPGA family. However, as shown in the figure below, Intel plans to replace its older Stratix, Arria, Cyclone, and Max FPGA families with architecturally compatible Agilex devices spanning the high-end, mid-range, and cost-effective (low-end) FPGA market segments. According to Intel, the Agilex 5 devices are more power-efficient than the company’s high-end Agilex 7 devices. They’re also somewhat smaller. You can expect that the Agilex 5 devices will also have fewer on-chip resources compared to the Agilex 7 devices. Note that the figure below omits the stratospheric, higher-than-high-end Agilex 9 devices with the 64Gbps analog converters that Intel announced a year ago. (See “Intel Takes Control of Communications Hill with Analog-Enabled FPGA Portfolio.”) Apparently, those parts exist in a somewhat different space/time continuum.

Intel plans to replace its Stratix, Arria, Cyclone, and Max FPGA families with various architecturally compatible Agilex devices. Image credit: Intel

For its part, Arrow has just gotten its first AXE5-Eagle boards back from the assembly house and has started to validate the design. The company is also developing tools, software, and reference designs for the board. The primary development tool will be Intel’s Quartus Prime Pro software suite. Normally, you need to purchase this tool from Intel, but the company has decided to make the software suite free for Agilex 5 design development.

Transferring FPGA configurations and compiled software for the Arm-based Hard Processor System (HPS) relies upon the Arrow USB Programmer2, which is included with the AXE5-Eagle board. The programmer interfaces to the AXE5-Eagle board through a JTAG port. Arrow is planning a series of future workshops to help design teams use this board. Workshop topics will include the Secure Device Manager (a new feature in Intel FPGAs), Designing with the RISC-V Nios Processor Core, and Migrating from Intel Quartus Prime Standard to Intel Quartus Prime Pro.

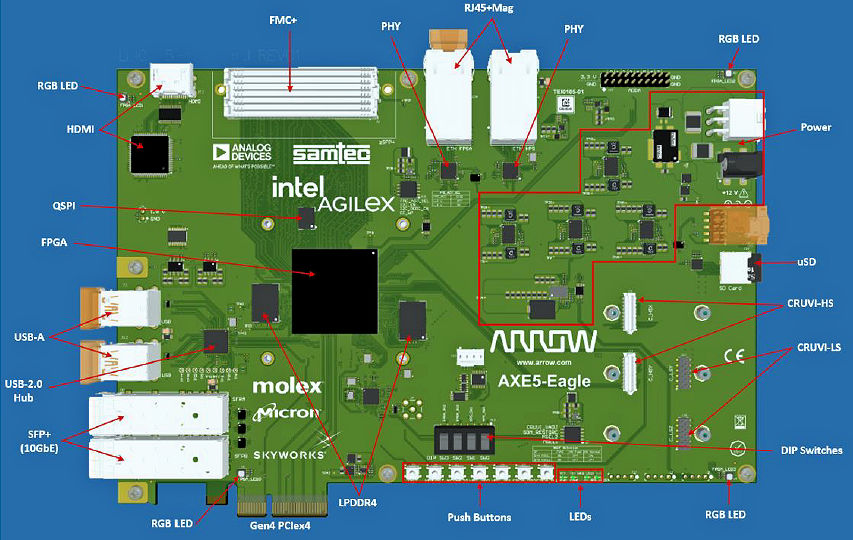

A board layout for the Arrow AXE5-Eagle board appears below:

The Arrow AXE5-Eagle development board incorporates many types of memory and on-board interfaces to ease development of systems based on Intel Agilex 5 FPGAs. Image credit: Arrow

Note that the board is designed as a PCIe card with a PCIe Gen4 x4 interface. The board also has two SFP+ cages for high-speed Ethernet connections, two RJ45 ports for lower-speed Ethernet connections, two USB ports, an HDMI port, an FMC+ connector, and four CRUVI (rhymes with “groovy”) ports. There are two CRUVI HS (High Speed) and two CRUVI LS (Low Speed) ports.

All these I/O ports are likely to be familiar except perhaps for the CRUVI ports. CRUVI is a relatively new expansion bus developed for FPGA boards by Trenz Electronic along with several other companies involved with FPGAs and FPGA boards, including Arrow and Samtec, which makes the CRUVI connectors. The CRUVI expansion bus is designed to serve many of the same functions as the larger and more expensive FMC+ bus, but it’s for simpler devices that don’t necessarily need the FMC+ connector’s 32Gbps serial transceivers. Trenz already offers several boards with CRUVI ports, including development boards for AMD Spartan, Intel Cyclone 10, and Lattice Certus-NX FPGAs, along with peripheral boards for debugging, loopback testing, memory expansion, and Ethernet connections.

The Arrow AXE5-Eagle board incorporates several types of memory and storage, including sockets for two 2Gbyte LPDDR4 DIMMs (one for the Agilex 5 HPS and one for the Agilex 5 FPGA fabric), a QSPI Flash memory to hold the FPGA configuration bitstream, and a microSD card socket to hold boot code for the Agilex 5 HPS. Arrow is developing two Linux distributions for the AXE5-Eagle board: a Golden system Reference Design (GSRD) using the Yocto build flow and a Raspbian system with support for a keyboard, mouse, and display based on the Raspberry Pi’s version of Debian Linux.

During a presentation about the AXE5-Eagle board, Arrow also briefly mentioned that the company is considering the development of two follow-on boards for smaller Agilex 5 FPGAs. One board called the AXE5-Falcon will be a smaller version of the AXE5-Eagle board with fewer on-board resources. In addition, Arrow is considering an entry-level AXE5 board to replace its Cyclone 10 and Max FPGA development boards. That board will be based on the smallest Agilex 5 E-series device, which Intel has said will have about 50K LEs.

Because Arrow already makes development boards for Intel’s Cyclone 10 and Max 1000 FPGAs, and because Intel has indicated that these devices will be superseded by Agilex devices, it seems nearly inevitable that Arrow will design new development boards for the smaller Agilex 5 FPGAs to replace the boards based on Intel’s current low-end devices. It also seems likely that Arrow will eventually be getting into the business of creating development boards for the Agilex 3 device family when those devices eventually become available. Although Intel has disclosed plans for creating this low-end Agilex 3 FPGA family, the company has been intentionally close-mouthed when it comes to details, so divining what boards based on these devices might look like would be pure speculation at this point.

Starting on January 1, you’ll need to substitute some other name for “Intel” throughout this story because Intel’s CEO Pat Gelsinger has announced plans to spin out Intel Programmable Solutions Group (Intel PSG) as an independent company at the beginning of 2024. (See “Intel plans to spin off FPGA group as an independent company nine years after buying Altera.”) It’s possible you just might see Intel PSG’s old name, “Altera,” return to the pantheon of IC vendors. I fully expect that this planned spinout will be good for Intel PSG, Altera, or whatever Intel decides to name the new company.

By freeing the new FPGA company’s top management from the corporate burden of worrying about how FPGAs fit into the world of Intel’s Xeon processors and by putting Intel’s internal processor Mafia at considerably more than arm’s length, the new independent company will be able to focus on competing against its old rival Xilinx – which has been strengthened by its merger with AMD – and against its newly invigorated FPGA competitors Lattice and Microchip, which have prospered over the last several years by exploiting Intel’s and AMD’s lack of attention to the mid-range and low-end FPGA segments. Meanwhile, Intel has more important things to worry about, such as building new fabs, keeping the process node train on the tracks, and taking back some lost processor market share from arch rival AMD.