I can tell you from the start, it’s impossible to capture a comprehensive history of the EDA industry in a few articles. However, I can’t find any sort of comprehensive history for the industry, so I’ve used multiple sources plus my own experience working for many EDA and EDA-related companies and covering the EDA industry as an editor to create this 8-part article series. Someday, someone will write an entire book on the EDA industry’s history. For now, I offer this article series, written from a personal perspective.

It can be very hard to pinpoint a date when an industry starts. Take semiconductors for example. Bardeen, Brittain, and Shockley switched on the first working transistor on December 16, 1947, but Bell Labs didn’t announce the event to the world until June 30, 1948, and did not start the semiconductor industry by licensing its transistor patents until 1951. So, where do you mark the start of the semiconductor industry?

Jack Kilby at Texas Instruments built the first prototype of an integrated circuit using a hybrid assembly technique on September 12, 1958. Then, Jean Hoerni entered his ideas for the planar manufacturing process into his lab notebook at Fairchild Semiconductor on December 1, 1957 and filed for a patent on May 1, 1959. Jay Last and his team at Fairchild Semiconductor powered up the first working monolithic IC based on Hoerni’s planar process on September 27, 1960. We’ve been using ever more advanced versions of Hoerni’s planar process to make ICs for more than 60 years. Where do you mark the start of the IC industry?

Unlike these examples, I assert that the EDA industry started on a very specific date: May 6, 1964. That was the inaugural day of the first SHARE (Society to Help Avoid Redundant Effort) Workshop, held in Cambridge Massachusetts and organized by Marie and Pasquale (Pat) Pistilli. If you’ve never heard of the SHARE workshop, you may know it by its contemporary name: the Design Automation Conference (DAC).

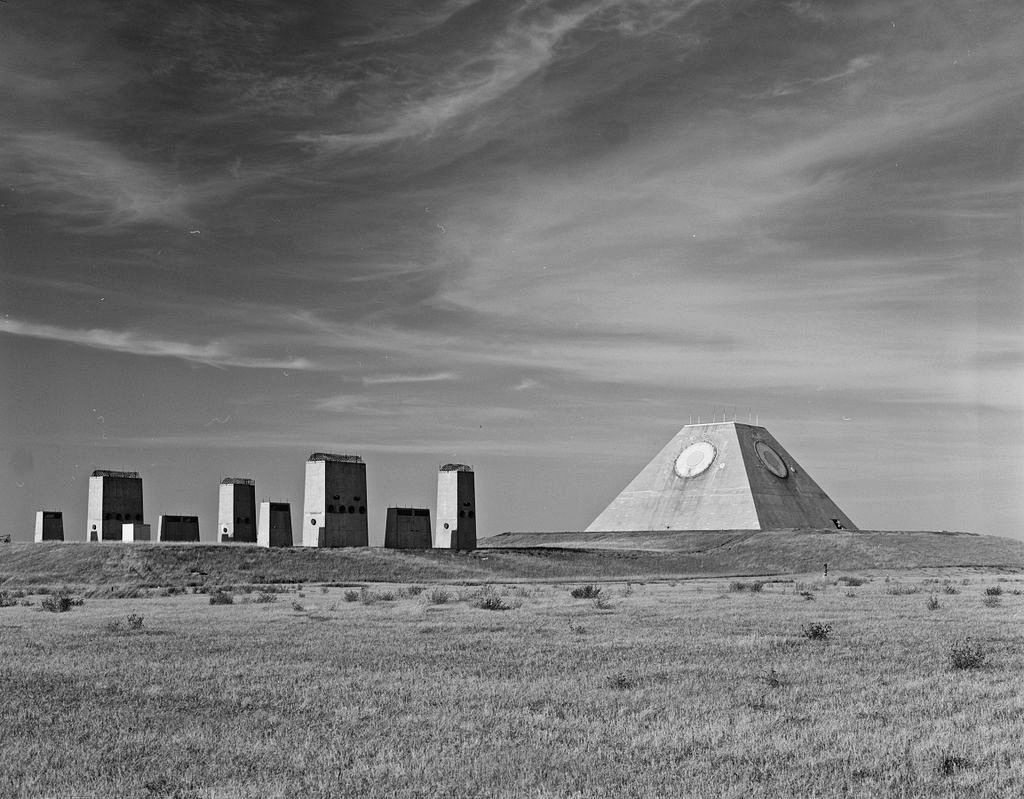

During the late 1950s and early 1960s, Pat Pistilli was working as an engineer with the Bell Labs team that was developing a new real-time computer for the Safeguard Program, an anti-ballistic missile (ABM) system that was under development for the US Army to protect the ICBM installations in the US from the threat of multiple incoming nuclear missiles. To reduce costs, Safeguard needed to discriminate actual nuclear weapons from decoys by using their slight differences in re-entry ballistics to differentiate between the two. To do that, the Safeguard Program needed a very fast computer to analyze the myriad signals from its land-based, phased-array radar system, which could track multiple targets simultaneously. The computer’s estimated required speed was 10 million instructions per second (MIPS), to be supplied by a multiprocessor system, with each processor operating at 1.5 MIPS.

In the early 1960s, the biggest, fastest computers were being constructed from individual transistors. ICs had not yet matured to the point where they were being used in systems. The Safeguard computer was built with small modules, each incorporating three or four discrete transistors. The modules were arrayed on 33×24-inch carrier boards and then interconnected by hand with wire-wrap wires. These carrier boards were plugged into refrigerator-sized units called frames and interconnected over a backplane. The refrigerator-sized frames for the Safeguard computer filled four rooms, according to Pistilli. (Bell Labs was familiar with wrapped-wire construction techniques because it used this type of interconnect for the electromechanical crossbar switches in its telephone switching offices. In fact, Bell Labs developed the technology and subsequently outsourced the wire-wrap tool manufacture to Keller Tools.)

The magnitude and complexity of the Safeguard computer project drove Pistilli to develop an automated system for laying out (placing) the 30 or so different standardized transistor modules on the carrier boards and interconnecting them. Conceptually, these modules resemble today’s standard cells used for ASIC design. Pistilli’s system – called BLADES (Bell LAbs DEsign System) – placed the modules on the carrier card and routed the Wire-Wrap wires to the individual modules. BLADES reduced the design, layout, and debug time required for each carrier board from six months to one. Because there were rules governing the way the wires could be routed, BLADES also included an early design rule checker.

The BLADES software ran on a tube-based IBM 704 computer, which could address 8096 36-bit words of magnetic core memory and had 32 magnetic tape drives. When Gardner Denver developed an automated wire-wrap machine that could automatically route, cut, strip, and wrap wires, Pistilli developed a controller that allowed the BLADES computer to directly manufacture the carrier boards using the automated Gardner Denver machine. Automated production of the carrier boards reduced fabrication time for the boards from a month to a day or two. BLADES was clearly an early EDA system.

The idea for an EDA conference resulted from Pistilli having a drink with a friend doing similar automation work at IBM. The friend’s name was Joe Behar, who was working on graphics displays at IBM. The two met regularly and realized it would be useful to meet with a larger group of engineers who were also working on similar challenges. Pistilli and Behar organized a Birds of a Feather session at a 1962 IEEE workshop held in Miami, which was successful enough for Pat and Marie Pistilli to underwrite the first SHARE Workshop in 1964. The workshop hosted more than 130 attendees and made a profit. By the third year, the Pistillis had dropped the name SHARE, and the event became known as DAC.

For more than 60 years now, DAC has served as a melting pot for people developing or using computers to address design and manufacturing challenges in the electronics industry. Initially, large systems manufacturers and semiconductor makers were writing their own software because there was no commercial EDA industry. In addition to Bell Labs and IBM, significant EDA software development was occurring at many universities, including the University of California at Berkeley (UC Berkeley), the University of California at San Diego (UCSD), the University of California at Irvine (UCI), the University of Southern California (USC), Carnegie Mellon University, the University of Michigan, MIT, the University of Texas at Austin, and Stanford University, just to name a few. Semiconductor makers that had reached a sufficient size such as General Electric, Intel, RCA, and Texas Instruments were also developing their own EDA software tools, and they created large design automation departments to develop and maintain these tools.

For example, at the end of 1974, RCA devoted an entire issue of “RCA Engineer” to the CAD and EDA tools developed at the company for IC and system design. These tools included: CRITIC – a design rule checker, PLOTS – a CAD artwork language, and ALACARTE – a computerized entry system for artwork.

In his book, “From Wild West to Modern Life: Semiconductor Industry Evolution,” Wally Rhines describes the design automation effort at Texas Instruments: “At TI, we considered our in-house EDA software to be a competitive differentiator. Much of the success of TTL for TI came from the ability to crank out one design per week with automated mask generation with the ‘MIGS’ system. Other semiconductor companies had their own EDA capability.”

Representatives from these diverse organizations found DAC to be an ideal place to share ideas about design automation, and to argue the merits of these ideas. Some of the more entrepreneurial DAC attendees then started to found companies that offered commercial EDA tools to the electronic systems companies and to semiconductor makers. The commercial EDA industry started in the 1960s but would not have a formal place to display their wares at DAC until 1984, twenty years after the event was founded. At my first DAC in 1986, the conference’s executive committee was already discussing the challenge of not letting the commercial exhibits turn the event “into a circus” after just two years of accommodating the exhibits. It was an open meeting, and, as I recall, the discussion was heated.

The Pistillis stayed close to DAC for the rest of their lives. Pat Pistilli chaired the conference in 1964, 1965, and 1966 and helped run the event in the following years. The addition of the commercial exhibits in 1984 convinced Marie Pistilli that DAC was now large enough to require full-time, professional management, so Pat Pistilli retired from Bell Labs and then co-founded MP Associates with Marie. Their company managed DAC for many years. The Pistillis retired from MP Associates in 2000. Marie Pistilli passed away in 2015 after being injured in an automobile accident. Pat Pistilli passed away in 2020. This year marks the 61st consecutive DAC, which owes its existence to the Pistillis. Together, Marie and Pat Pistilli can easily be called the parents of the EDA industry.

(Note: Hall-Erickson took over management of the exhibit part of the DAC in 2018.)

References

Alberto Sangiovanni-Vincentelli, “The Tides of EDA,” IEEE Design & Test of Computers, November–December 2003

Paul McLellan, Pat Pistilli: the first cell library, the first computer-printed label and more

Clive Maxfield, Quaffing a beer with The Father of EDA

Bryon Moyer, Can Do: Pat Pistilli Shows How Problems are Solved

DAC ’64: Proceedings of the SHARE design automation workshop

RCA Engineer, December/January, Volume 20, Number 4, 1974/1975

Wally Rhines, “From Wild West to Modern Life: Semiconductor Industry Evolution,” SemiWiki LLC, 2019