For two decades, the FPGA market has been a well-balanced duopoly – a yin and yang cocktail of equal but opposing forces arranged in perfect discordant harmony. Xilinx and Altera have acted as a matched pair of mutual predators in the evolution of a market that has played an important role in the electronics ecosystem. For every Xilinx action there was an equal and opposite Altera reaction. Each Altera thrust was met by a Xilinx parry followed by an Altera riposte.

The foils in this twenty-year fence-o-thon have clearly been semiconductor processes. There were huge rewards – in both cash and market share – to whichever company could successfully harness each new process node first (and we mean actually harness – defined as delivering working silicon in volume to their customers, rather than “marketing harness” – defined as being the first to issue a press release bragging about the new node.) The two titans have generally taken turns winning at each process generation, and the market share line has slowly swayed back and forth like a tide with a two-year time period.

Playing the role of armor in this fencing match were tools, IP, and services. During the majority of the time when the two warriors’ silicon offerings were at parity, they waged an arms race in design tools, IP offerings, and AE armies. Given two equivalent FPGAs, customers would tend to flow towards the supplier with the smoothest flow – offering the least risk and resistance on their path to a working design.

The result of all this has been a sizzling ride down the semiconductor slide – with increasing stakes at each turn. It takes a nine-digit sum to pop out a new FPGA family on today’s hottest processes – a fact that has safely repelled most insurgents. If the pricey process moat didn’t keep competitors out, they were summarily crushed by the overwhelming advantage the big two had in tools, IP and AE support. The FPGA fortress – although a house divided – was well defended.

Now, however, there is a fissure in that wall, in the form of new FPGAs from Achronix. Achronix is attacking the big two head-on and hitting them directly with their own weapon of choice – process advantage. Achronix has partnered with Intel to produce new FPGAs based on Intel’s 22nm Tri-Gate (we’d call them FinFETs) transistor technology. With both Xilinx and Altera currently on TSMC’s 28nm planar CMOS processes, we figure this gives Achronix close to a 2- process node advantage with these new FPGAs – one for the smaller geometry and one for the new “3D” Tri-Gate transistors. These two advantages should conspire to allow Achronix to build FPGAs with higher density, lower power consumption, and higher speeds – at a lower unit cost than the two big competitors.

Achronix has also gone directly at the heart of the big companies’ market stronghold – including the golden goose of the FPGA market – communications and networking. The big two have spent the last several years working to expand the FPGA market. Since they had gobbled up communications and networking, there was little to be won by small back-and-forth swings in market share there. The big gains were to be had by growing the FPGA pie into new applications – so new features were added to FPGAs aimed at expanding them beyond this traditional stronghold.

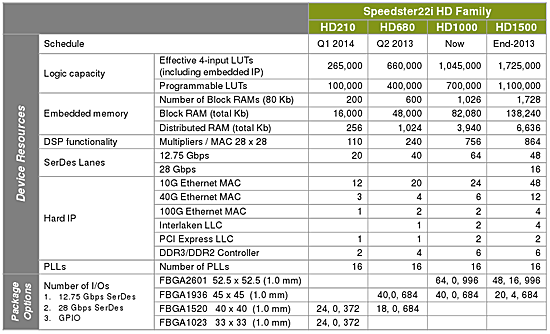

It is in these new features and lack of market-specificity that Achronix saw a second vulnerability in the big two. Achronix decided to populate their devices with optimized, hardened IP blocks for many of the functions important in the core FPGA market. They added up to two hard 10/40/100G Ethernet MACs; two 100G Interlaken; two PCIExpress (with DMA) gen 1/2/3 – x1, x4, and x8; and six DDR3 2.133 Gbps. All of this hard IP accomplishes several things: first, it makes those functions faster, cleaner, more reliable, lower power, and dramatically easier to add to your design (compared with soft-core versions of those same functions implemented in FPGA LUT fabric), and second, it saves all the LUT fabric that would have been used for those functions for other uses. Achronix figures that their stock of hard IP is worth about an additional 375,000 LUTS. Add that to the advantage they have on the actual LUT fabric from the gate size and FinFET transistors, and the net effect should be formidable.

Achronix claims, in rough terms, that the net-net of this is that they’ll be offering customers FPGAs with densities equivalent to the big 2 vendors’ high-end devices, but at half the cost and with half the power consumption. If that turns out to be a fit for your application, those are compelling advantages.

The only remaining hurdle for Achronix to conquer will be the tools, IP, and support wall. Achronix says they are ready to prove themselves on that front as well. The company says their “ACE” design tool suite – based primarily on Synopsys tools in an Eclipse Open Source Foundation platform – has been installed at over 500 customer sites over the past several years, and it is well proven and stable. It’s worth mentioning what all those customers were doing over those years before Achronix launched this new family. The company was previously known for their more-radically-designed asynchronously clocked FPGA fabric. In those devices, the company used what they called a “picoPIPE” architecture that allowed the fabric to be clocked at much higher frequencies. The currently-announced Speedster 22i family does not include the picoPIPE architecture, but the company says that remains a possibility for future offerings.

Achronix says their advantages from partnering with Intel extend beyond the process superiority. They point to things like their entire manufacturing chain being US-based, and the one-stop-shopping for fabrication, testing, packaging, and qualification. For some customers, these will be important considerations as well. It is also interesting to watch Intel’s role in this event – as the company has long been known for excellence in semiconductor fabrication, but it has very little experience in operating as a merchant fabrication service. The difference is a bit like the difference between being an excellent cook and running a successful restaurant. When you have customers to serve and a service business to run, you have to be on top of your game in a lot more than just the kitchen.

The Achronix Speedster22i family has four members, and the first of those (the 1-million LUT capacity HD1000) is shipping to customers now. In historical terms – if we look at startups that have attempted to crack the stronghold of the big two – the fact that working silicon is in customers’ hands puts Achronix amongst the elite of the elite. Other established competitors in the FPGA market – Lattice Semiconductor, Microsemi (Actel), QuickLogic – have all gone into specific smaller segments of the FPGA space and have not made a concentrated effort to go after the big two on their home turf – high end FPGAs. The only other competitor worth watching at this point is Tabula – who is developing their own high-end FPGAs based on the same Intel 22nm Tri-Gate process that Achronix uses. We’ll know more about that horse when it shows up at the starting gate.

If Achronix has the advantage they claim with the Intel 22nm Tri-Gate process, it could be a very long and difficult road for the big 2 FPGA companies to overcome. Both Xilinx and Altera have already announced plans for their next families to be based on TSMC’s 20nm planar transistor process, and products based on that process are likely 2 years away. Once there, the industry scuttlebutt is that 20nm planar will be a bit of a dud – with the incremental advantages compared with 28nm planar being smaller than with previous node jumps. Most experts agree that some form of FinFET (or other 3D structure) transistor is needed as we pass through 20nm, and if current speculation is accurate, that won’t happen for the big 2 FPGA companies for another two process leaps – or as much as four years from now. That scenario could allow competitors like Achronix to make serious dents in the big FPGA companies’ market shares.

NOTE: Just at press time for this article, Altera announced they will be partnering with Intel to produce FPGAs based on Intel’s upcoming 14nm Tri-Gate (FinFET) technology. Regardless, Achronix should have at least three years shipping FinFET-based FPGAs before either of the major FPGA vendors is ready.

Of course, one should never underestimate the wherewithal, resources, determination, and capabilities of Xilinx and Altera. They have both proven time and time again that they’re able to overcome incredible hurdles – both technological and competitive – in order to prevail and retain their lucrative market positions. That should make watching this latest attack an even more interesting show.

Do you think Achronix will be able to translate their current advantage in process technology with Intel into market success in high-end FPGAs?