By all accounts, the jury has heard the evidence, deliberated, and rendered a verdict: the future is FinFETs. Despite some other folks still trying to remain relevant.

But… just when you think that the case has been settled and all of the affected parties can achieve closure, the decision gets appealed. This particular appeal comes courtesy of startup SuVolta. They’ve got a different way of solving the world’s transistor problems, and it doesn’t require a third dimension.

To help put this into perspective, let’s back up and review the nature of the problems that are forcing us to something other than the kind of scaling we’ve been doing for the last few decades.

It’s hard to imagine it, but transistors and the circuits they populate do work. (“Work” in the “getting something done” sense, not in the, “Hey, this one works, ship it!” sense.) In order to muster the energy to do that work, they gotta eat. The more work they do, the more energy required, so the more they eat.

Which means that taking a piece of silicon and telling it to do more work than it used to do will require that it eat a lot more – unless you can find a way to make it more efficient so that it can do more work without sharpening its appetite yet further. And this, of course, has captured the lion’s share of process development over the last few years. It’s no longer about making things go faster; it’s about getting the transistors to work harder while moving them towards more of a starvation diet.

We’ve done that both by reducing the voltage levels and by shrinking the gates. The lower voltage levels mean that you’re working closer to threshold, but, even if you push the threshold down a bit, you’ve still got this “subthreshold slope” issue – how solidly does the transistor turn off when you go below threshold? All too often, the answer has been, “Not very solidly.”

OK, so you try to design around that. But it gets worse. The doping in the channel region is achieved by blasting a bunch of dopant atoms into the silicon with the equivalent of an atomic blunderbuss. The number of atoms? Well, that’s going to vary. If you’re depositing millions or even just thousands of atoms, then one or two more or less doesn’t matter; it’s mice-nu… um… noise.

But what about when you’re only implanting a dozen or two atoms? Now that “plus or minus one” thing makes itself felt. And, unless you’re going to find a way to inject atoms one at a time for a precise count (and do so in a way that doesn’t bring production to a crawl), you’ve got to live with the fact that your channel doping will vary. And so you have to guardband your design to capture the worst case.

So part of the critical idea with FinFETs, in addition to getting better control of the channel by almost surrounding it with a gate, is to eliminate doping from the channel. No doping? No fluctuation. One of the funny things about such statistics: one and above are approximate; zero is exact. (OK, not counting any trash already inside the silicon.)

Which kind of makes you rethink why we were even doping the channels in the first place if we could get away without it: the purpose is to establish a desirable VT. No doping also means no threshold control. So, according to SuVolta’s Jeff Lewis, companies are surreptitiously starting to do some doping on the FinFET fins to tweak the threshold. Shhhhhh…

So FinFET channels solve the random dopant fluctuation problem (unless you start adding dopants again). For a pristine gate, then, FinFETs should have less variability. Except for the fact that the fins themselves vary a lot in their as-built geometry – which is why single transistors will typically use multiple fins to average out those variations.

SuVolta has a different way of addressing this: they’ve got their own new transistor. Which is pretty ballsy: it’s not every day that a fundamentally different transistor structure is given a commercial run for its money.

And they can’t do it on their own; it’s not like they’ll simply be selling transistors at the Quickie Mart (“Would you like Fry’s with that?”). They’ve got to get IDMs and foundries to sign on. Which takes time and patience. FinFETs already have Intel as a sponsor, and the foundries are following suit with their own FinFETs, albeit a couple nodes later. Even without the foundries, Intel has the luxury of going it alone if they want; SuVolta simply can’t.

So what is this new device that has them slogging down such a hard road? It’s not a 3D transistor; it remains planar and will look familiar in its broad strokes to anyone who’s used to “standard” transistors. The trick is that they use an undoped channel – while still allowing control over the threshold voltage.

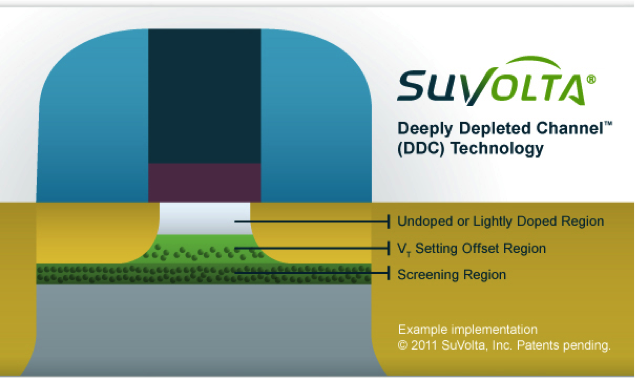

Their structure, which they call a “deeply-depleted channel” transistor, is shown below. It consists of three layers: the undoped channel itself; a layer for setting the threshold; and a “screening” layer that provides a controlled edge for the depletion region. There’s actually a layer below that used to isolate the device and prevent punch-through.

Courtesy SuVolta

Note in particular that the transition between the middle and the undoped layers is pretty sharp. If the threshold-setting and screening regions are simply implanted, it’s hard to imagine that you’d get that nice, sharp edge. And you might therefore think that the nice, sharp edge was more for the convenience of the graphic artist making the drawing. But, in fact, it is implanted and it is that sharp: the undoped layer is epitaxially grown after the implants are done. Isolation trenches are then cut after the channel is in place.

The VT-setting implant is where you get control of the threshold. And a design could employ transistors with many different VTs simply by selectively masking the transistors and using a different mask and implant for each VT. In theory, it would seem that you could have no limit to the number of different VTs available.

So you get an undoped channel (which, by the way, not only removes dopant variation, but also improves mobility since there aren’t all those impurities in the way), and you get a way to trim your threshold.

If you’re feeling particularly aggressive as a designer, you can optimize your power and performance with back-biasing or body-biasing, although SuVolta stresses that designers don’t need to use back-biasing – it’s simply another tool if they want it. Ideally, you want forward biasing when the transistor is on for better performance; you want a reverse bias when the transistor is off to reduce leakage (for an n-channel device; the opposite applies for a p-channel transistor). You could decide on some happy-medium biasing level that optimizes the balance between performance and leakage.

Alternatively, you could use what they call “adaptive” body biasing. This could be used to correct for systematic variations in threshold. If a particular die has a threshold that’s off center, then, rather than throwing it away or binning it as a cheaper version, you can trim it back by adjusting the body bias. Such tweakage would be done at test.

For really gung-ho designers, you can implement what they call “dynamic” body biasing: change it on the fly. Before you get carried away with this, I can’t imagine that the bias could flip around quickly enough to match an actively switching transistor. But, short of that, if you have a core or some other block on the chip that’s going to sleep, for example, then you could bias the block for low leakage. When it wakes up again, you can change the bias in favor of better performance.

In addition, dynamic biasing could be used to correct for gradual shifts in thresholds as the device ages. Granted, this would be a more sophisticated circuit, since it would have to monitor VT and then set a suitable back-bias voltage (it’s not simply a forward/backward digital decision). But… it’s doable. (And it’s beyond what most designers are doing now.)

So that’s their idea in a nutshell. And nutshell stuff is pretty much all that’s publicly available now. They’re in this period of proselytizing to folks with fabs, not all of whom want to acknowledge publicly what they’re doing.

So, for instance, most of the public discussions of anything concrete involve nodes like 65 nm, which aren’t particularly aggressive. Which spurs the obvious question, “Does this thing scale? Is it relevant at, say, 14 nm?” The answer to which seems to be, “Um…. Stay tuned.”

Is this going to knock FinFETs off the block? Well, SuVolta certainly isn’t going that far in their messaging. Intel, after all, is Intel. They’re practically their own planet, so reality suggests that if Intel is banking on FinFETs, then FinFETs are happening. But will the DDC transistor challenge it outside Intel?

Mr. Lewis suggests that the DDC has particular advantages for low power (or better performance for a given power level) or for analog, given its superior matching capability. It also provides better drive current and is likely to do better in SoCs that need a variety of transistors. And it’s less complex to make than the finicky FinFET.

FinFETs, on the other hand, may continue to prevail in high-performance-no-matter-what-the-power applications. That would suggest Planet Intel in particular.

SuVolta claims that they’re making good progress in their integration work with different companies, and that announcements will be forthcoming. For right now, we sort of have to take their word for it that things are coming along nicely.

In other words, the appeals judges are deliberating. We await their ruling.

More info:

A new transistor is trying to gain traction in a neighborhood near you. Would you use it? Why or why not?

I always suspected that somebody might try to find a clever way to extend planar CMOS to 20nm and below – just I as suspected (hoped?) back in the late 1980’s / early 90’s that some clever optical lithographers would find a way to avoid using X-Ray lithography below 0.5um. Fortunately for the semi industry, the optical lithographers did.