[Editor’s note: this is the third and final installment in a series of articles on ideas for revitalizing Silicon Valley. The prior installment can be found here. Your comments – in agreement or not – are welcome.]

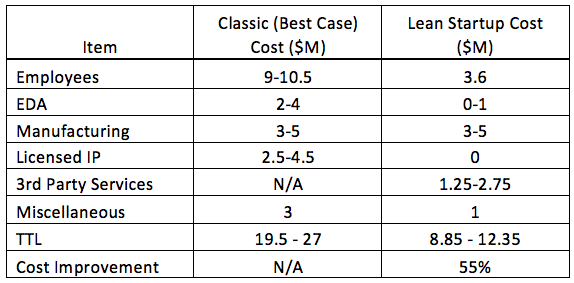

In the first installment of the “Revitalizing the Chip Startup Environment” article series, the Lean Chip Startup (LCS) model was introduced as a new methodology for managing the operational and financial aspects of semiconductor ventures. In the classic Geoffrey Moore chip model, the venture required anywhere from $25M (best case) to $100M+ (typical) and stood a 5%-10% chance of any sort of success. The LCS methodology, by contrast, offers a 90%+ success rate with an investment anywhere from 30% to 40% lower than the classic case.

Of course, $16M is not exactly pocket change, and it would be prudent to seek additional cost savings to further improve ROI. So what would be a good choice for further cost reduction? The largest single item on the LCS model is the generic IP obtained through licensing. With some effort and planning, the costs for that IP can be reduced dramatically and further reinforce the trajectory of success for chip startups if VC’s open themselves up to partnering with IP vendors.

The Chip IP Industry

The sector of Silicon Valley that has experienced the most dynamic change over the last decade is clearly the IP segment. The evolution of this sector has broadly followed the same historical roadmap as the rest of the electronics industry. In the 70’s and 80’s, component suppliers such as TI, National, AMD and Intel built tiny ICs in PDIP packages (in enormous volumes and thin margins )that were bought by systems houses such as IBM and DEC, who soldered the components onto PCBs, wrote a software stack and combined them as a computing system that would sell at a high margin. As time passed, the systems houses sought to reduce cost and increase quality and reliability by pressuring the IC makers to integrate. With higher levels of integration arose the need to start paying serious attention to the software aspect of electronics – hence the birth of the SoC. Along with system houses pushing complexity down the supply chain came significant value transfer, as successful SoC makers, CPU suppliers and PLD vendors saw their margins grow to 45%-65%. Pursuing ‘value concentration’ on their own initiative, it was the PLD vendors who led the fabless charge, as they eschewed fixed plant costs of fabs and assembly lines in favor of value-add from design and applications expertise to drive margins up to 80-90% for their very newest products. SoC makers followed suit, with their emphasis on core competency and value-adding technology raising margins and system level sophistication.

One can see that the same migration of complexity, system-level sophistication and value transfer has proceeded down the supply chain from chipmakers to IP firms. SoC developers have thinned out their hardware teams to the bare essentials for developing, enhancing and maintaining hardware in favor of growing their software teams (to the point that software developers often outnumber hardware engineers by 3:1 or more) . Generic IP development (standard cell libraries, SRAM compilers, I/O libraries, SERDES, PCIe, USB 3.0, Ethernet PHY/MAC, CPUs, DSPs, peripherals libraries, jelly bean analog such as PLL, DLL, most DACs and ADCs, and so forth) has been left to companies specialized in the design, delivery and support of such products. In fact, generic IP has come to dominate chip area over chipmaker ‘secret sauce’ by an average 80%/20% ratio.

One can see the results of this most dramatically in the two premier IP suppliers in the industry today: ARM and Synopsys. Compare the ARM of 2002, at the final collapse of the dotcom bubble, to the ARM of today: a company with a vast array of sophisticated synthesizable CPUs – including multicore and superscalar offerings, with a variety of application-specific extensions – and accompanying standard cell and I/O libraries, memories, peripherals, emulation systems, toolchain and even a fourth-generation hierarchical bus architecture (AMBA) that long ago became a ubiquitous industry standard.

Even higher levels of system sophistication and IP selection (with a greater emphasis on standard function digital and analog/mixed-signal blocks) are evident in the Synopsys DesignWare offering, including dedicated tools for configuring cores and crafting AMBA-based bus hierarchies, audio and video software, a plethora of interfaces for memory, storage, multimedia and other functions, verification IP, and even an in-house CPU offering in the ARC family of 32b embedded CPUs . The DesignWare portfolio of technology also includes backend design services, extending Synopsys’s participation in the chip development ecosystem to the system integrator segment. Further leverage stems from the company’s overall dominance in the entire EDA toolchain and accompanying influence on front and back end methodologies for chip development.

A New Industry Alliance

To put it simply, VCs bring funding, and IP vendors bring essential technology. Both want to make high returns from a rejuvenated chip startup sector. The key to bringing this about is for them to become partners.

So how would IP and VC firms work together, and to what benefit for each party? The way forward becomes clear once mutual risks, rewards and advantages are recognized.

A few remaining VCs still engage in some chip startup funding. But despite the informal relationships many of them have with each other, there is still an overwhelming tendency for VCs to ‘go it alone.’ However, in order to revive Silicon Valley’s chip industry through disruptive invention, old paradigms must be recognized as being broken and hopelessly outdated. Thus, a change in operating practices for VCs is in order, as it is for the entire chip sector.

The first thing for venture firms to do is pool a portion of their resources, giving them collectively greater leverage as a group – and also spreading the risk. Five VCs can form an “IP fund” with $2M contributions, creating a $10M fund. But the fund will be incomplete without bringing IP vendors in as partners. Their contribution would come from providing IP to the VCs’ startups in return for current and future financial & business considerations. Of course, the devil is in the details – how would such alliances take shape to the benefit of all concerned?

A VC Alliance with ARM

The $10M fund could be applied to a four-year licensing contract with ARM, who would in return offer their entire IP portfolio for use by the chip startups of each VC. Of that $10M, 25% of it could be devoted to providing engineering support to the chip startups. $2.5M divided five ways over four years at a nominal rate of $250/hr means each VC can parcel out 500 hours each year as they see fit.

Any startups under this VC fund ‘umbrella’ would have to begin their operations during the term of the license, and the entire ARM portfolio – including supporting products and services, such as tools, emulation boards, debug probes and the like – would be ‘free’ for the first generation of the startup’s products. The contract could include provisions that coverage under the license would expire once a particular startup achieves success, either through IPO or acquisition, as well as requiring any second generation of product development to be covered under a new licensing agreement.

How does this serve the strategic advantage of the VCs and their startups? Clearly there are profound benefits:

- No longer will each startup have to cough up cash for generic IP – they get it ‘for free,’ along with service and support, for 90%-100% of their generic IP needs. This allows them to focus more time and resources on their disruptive technology and on working with the system integrator ecosystem, improving time to market (TTM) and increasing the likelihood of ultimate success further – all music to the ears of VCs.

- VCs would realize an immediate 25-30% cost savings per funded startup.

- ARM has the largest third party ecosystem of any IP vendor.

But how would ARM benefit from such an arrangement? After all, in the past several years ARM has developed a ‘bundling’ model on 4-year term licenses for anywhere from $4M to $5M. If the VC Alliance members each bring between two and four startups in that same term, ARM would have to supply their entire product portfolio to as many as 20 chip startups for the price of two independently licensed bundles.

Yet the advantages to ARM participating in the alliance are far greater:

- The LCS model will significantly increase chip startup activity, and thus the total available market (TAM) for ARM IP products. By supporting this initiative, ARM increases its own available market for licensing.

- Rather than compete at each individual account, hoping to coax funds out of single startups, ARM would capture the entire sample available market (SAM) supported by this VC fund in one fell swoop.

- By locking out these startups from all other IP vendors early on, and with the 90%+ likelihood of each startup achieving success through the LCS model, ARM would find itself in the catbird’s seat once the licensing terms lapse and each startup is accountable for its own IP licensing costs.

- ARM would gain ‘crystal ball’ insight into chip technology trends to guide their own product development efforts.

A VC Alliance with Synopsys

The advantages to both VCs and Synopsys in a partnership might be even greater than those with ARM. Synopsys has an even more abundant embedded portfolio. Furthermore, Synopsys would have an avenue to promote its ARC processor line and backend engineering design services. For their part, the VCs can coax an additional $1M in funding savings for each startup by having Synopsys roll in the limited amount of EDA tools support required by each startup (limited to synthesis, timing analysis and simulation tools for front end design work.) Combined with the realizable cost and TTM savings outlined in the second article in this series concerned with ESL and Verification, cost savings reach a whopping 55% for the LCS model, reducing the total bill for each startup to roughly $10.5M and reinforcing the goal of a 90%+ success rate.

Alternative IP Partners

There are advantages to the VCs, however, to passing up on the ‘one stop shops’ that ARM and Synopsys offer as virtual ASIC houses. A careful scan of the second- and third-tier IP vendors reveals a number of companies who, lacking the market presence and third-party ecosystem of ARM or Synopsys, nevertheless have first-tier products available at lower prices than the market leaders. MIPS and Tensilica are clear examples of this in the CPU IP space. Other such high-quality vendors for digital cores, analog/mixed-signal blocks (including SERDES), standard cell and I/O libraries, memories and EDA tools are out there as well – Cadence in EDA tools, Mentor in EDA and IP, Dolphin Technology for physical IP, CEVA for embedded DSP, Imagination Technologies for multimedia processors, and many more.

Though assembling a more polyglot selection of IP vendors for the alliance places an additional management burden on the VCs (particularly when it comes to apportioning the yearly 500 hours of engineering support), the extra administrative effort can be a worthwhile tradeoff for expanding the IP selection available to supported startups, and it will likely bring some cost savings to the fund as well.

A New Approach for Changing Times

VCs have long been self-reliant, carefully managing their investment funds while using their own technical and business acumen to select technology ‘targets of opportunity’ and seeking to staff them with screened executive and engineering talent in hopes of maximizing their chances of success.

But the ‘lone wolf’ approach now leaves even the strongest VCs vulnerable. Chip startups in China have received massive provincial and national government support without the national repercussions of ‘Solyndra’-like debacles. Going it alone is simply no longer feasible.

Thus, the future for venture funds lies in partnerships. Spreading risk and pooling resources maximizes VC ROI. This new approach, combined with the LCS method, will open the way for VCs to finally and completely fulfill their role as incubators of revolutionary technology for which they have strived over three decades.

Authors:

Peter Gasperini – VP of Business Development, Markonix LLC; previously President and GM of Iunika North America, with 22+ years of experience in Silicon Valley with ASIC, FPGA, embedded microprocessors and engineering services.

Contributors (abridged):

Amit Dhir – Director, PwC Advisory/Management Consulting; previously, VP of Vertical Markets at MIPS

Rakesh Patel – Consultant, Strategic Initiatives at Global Foundries; previously Sr. Director R&D IC Design at Altera

Do you see a “generic” IP giveaway as a means of making it easier to attract investment?