Just three weeks ago, Xilinx announced the latest version of their PlanAhead software, asserting among other things that they had simplified the daunting task of partial reconfiguration. We listened, and went so far as to include a section on this potentially ground breaking technology in our February 7 article on the subject (see article). We acknowledged our hesitation to get too excited about the idea, feeling that it would take a very brave soul indeed to jump in and give it a try. At the time, it felt like the equivalent of hanging your hat on academic fantasy. And even if it was real and it did work, you’d have to be some kind of Samurai black belt FPGA ninja to use it. However, after last week’s announcement on this same topic, including a full-blown real world application that takes advantage of this technology, perhaps we’ll need to apply the notion of partial reconfiguration to our own editorial archives.

Xilinx has partnered with Montreal, Canada-based ISR Technologies to deliver the industry’s first commercially available kit for a Joint Tactical Radio System (JTRS) software-defined radio (SDR) that uses two Xilinx technologies – embedded Virtex-4 FX FPGAs to leverage SoC capabilities, and partial reconfiguration using PlanAhead 8.1 software. Their numbers show that using this kit can result in a 2-3X reduction in both system power and cost. Speaking of power and cost, these are two of the biggest challenges facing the JTRS SDR industry. On the power side, a typical model for a four-channel JTRS SDR radio could use as many as 12 DSPs, not including memory or other types of devices. That means that signal processing alone could burn more than 70W. Although systems are often built in a modular fashion, that’s still a heck of a lot of power. Regarding cost, for the example system above you could be looking at a price tag in the thousands of dollars.

SDR is a killer app for unique capabilities that you can find only in an FPGA. In SDR, you have DSP algorithms that have to be accelerated into hardware to reach performance goals, and you have to be able to change those algorithms on the fly. The FPGA becomes almost a critical enabling technology for SDR. There may be other ways to meet the SDR challenge, but not as well as you can with an FPGA.

Now, what if you need to reconfigure the FPGA in your SDR while it’s still running? For an SDR with multiple channels, you may want the flexibility to reconfigure part of it without shutting down the entire system. This creates a scenario that puts an extreme demand on the system for partial reconfiguration. Remember, this is cutting edge stuff–very hard to do, and chock full of super complicated issues. If you’re handling it without the help of the SDR kit, there are several things to consider. First, you need to set off a safe physical section of the device, and you have to define all the inputs and outputs from that part. Those I/Os have to be fixed regardless of what new stuff gets put into that partially reconfigured area. Then, when you’re initially programming your FPGA, you need to protect that area that you set aside. You can designate it to be a big routing block for the rest of the FPGA, or you can allow the rest of the FPGA to route through that area, but that means any time you partially reconfigure it, you have to maintain connections through that area. Lots to think about. Which brings us to the kit…

The Whole Kit and Kaboodle

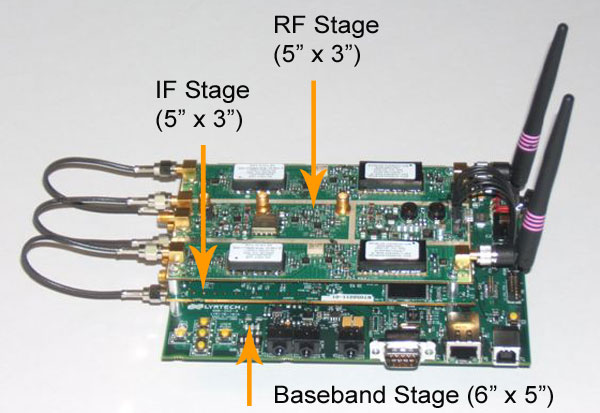

Xilinx and ISR Technologies have created a JTRS SDR kit that contains all the hardware and software that you need to go straight through to production. As shown in Figure 1, the kit includes two SDR modems with two voice over packet phones to create a communications link between the modems. Two computers with webcams are attached, enabling you to have streaming video moving from one webcam through the laptop and the modem and onto the screen for display on the other laptop. Both streaming video and voice come as part of the kit.

|

|

Figure 1. Xilinx-ISR Technologies Virtex-4 FX JTRS SDR Kit (image courtesy of Xilinx)

|

There is also a Xilinx Virtex-4 FX60 in each of the modems, and they’re supporting two waveforms: one for streaming video and one for voice. Through the kit’s graphical interface, you can instruct the radio to load a waveform. It will load that waveform while maintaining static circuitry. It’s actually loading the waveform into that “safe” part of the FPGA mentioned earlier. Once it’s loaded, you’ll see the output on the laptop. Without partial reconfiguration, if you then wanted to make a voice call using the voice over packet phones, you would have to reconfigure the entire FPGA, which would require you to shut down the streaming video. With the technology in the JTRS SDR kit, however, you can maintain the first waveform, go back into the graphical interface, and load the other waveform. It gets loaded into another safe part of the FPGA that’s available while maintaining the static circuitry and the other waveform. Once the second waveform has been loaded, you can make a call from one voice over packet phone to the other while maintaining the video. Voice and video can work in tandem, but you can also shut down one without affecting the other.

“Previously, if you wanted to have this kind of functionality to support two different types of links for voice and video, you needed two devices,” said Manuel Uhm, senior DSP marketing manager at Xilinx. “You would have one set of hardware in one slot supporting the voice, and if you wanted to then have video while maintaining the voice, you would have to use a second slot with a second set of processing resources. We’ve taken all of that and put it on a single device.”

The Xilinx PlanAhead software is graphical, and gives you the capability to define and change the size and shape of the modules that are being partially reconfigured. You can automatically get access to your area budget to understand what resources are being consumed by each module, which can help you do placement to maximize your resource utilization on the FPGA. Additionally, PlanAhead performs automatic design rule checking. “Using a traditional approach, you would have to build your entire design, run it, and see what breaks,” continued Uhm. “Now, PlanAhead does all the design rule checks. It may still break things in your design, but if it does, you know that it has something to do with the way you’re doing the application, not the way you’ve architected your partially reconfigurable module.” PlanAhead leverages the Xilinx ISE back-end tools, but provides the designer with a graphical interface to do the design.

A key part of the kit is a reference design that people can use as a starting point. The kit includes the waveforms as source code. It comes with all the hardware to run both the voice and the video. You can choose to either modify the designs or perhaps create your own design. The kit uses Compact Flash to load the partial bit stream, so you can easily make changes to the waveform and see how it runs on this ready-made platform.

Another differentiator for this kit is the SCA-Enabled SoC. The classic FPGA integration story plays here. Typically, if you look at a DSP node within a modem, you would have an FPGA coupled to the DSP and a general-purpose processor. Using the Xilinx Virtex-4 FX device, you can handle all those types of processing in a single FPGA. By taking this approach of having an SoC using partial reconfiguration, the hardware that’s being reconfigured to support the different waveforms looks just like software. It all runs on an RTOS, using CORBA, and it leverages capabilities that you could previously leverage only on a general-purpose processor.

The JTRS SDR kit is priced at $75,000 USD and will be available in late March. The future looks bright for this type of technology, for JTRS applications, and beyond.