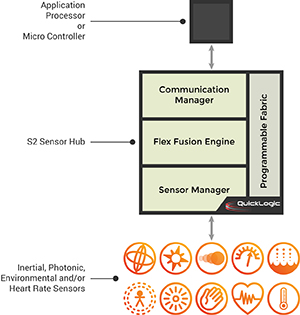

We’ve spent a bit of energy in the past looking at QuickLogic’s approach to a low-power sensor hub. Well, they’ve just introduced a second round, and the obvious question is… what’s changed?

They list some of the current capabilities, but the obvious questions are, how does this compare to the first one, and how did they make this happen?

Fundamentally, this hub has more horsepower than their first one. So they can do more work. They had a basic pedometer in their first hub; with this one, they have an “enhanced” pedometer that can now discriminate between walking, jogging, and running, while counting individual steps.

As it turns out, however, most of the capabilities on their second go-round weren’t possible on the first one. They noted features like IrDA remotes, barcode transmission, and pulse-width modulation (PWM) for dimming displays – none of these could be done by the first hub.

So how did they do this? Two things. First, they looked through some of the critical functions to see which things weren’t likely to change anytime soon (or ever); they hardened those into dedicated gates. That sped things up and lowered power.

But they also made some process changes. They didn’t go into the details of what changed, but the goal was yet lower power. After all, adding more capability usually has a power cost, which they have to fight since power is such an important part of their message. As it is, they’re claiming as low as 150 µW – even as they’ve added programmable logic and processor capacity, algorithm memory, and data buffer memory.

Image courtesy QuickLogic

You can find out more in their announcement.