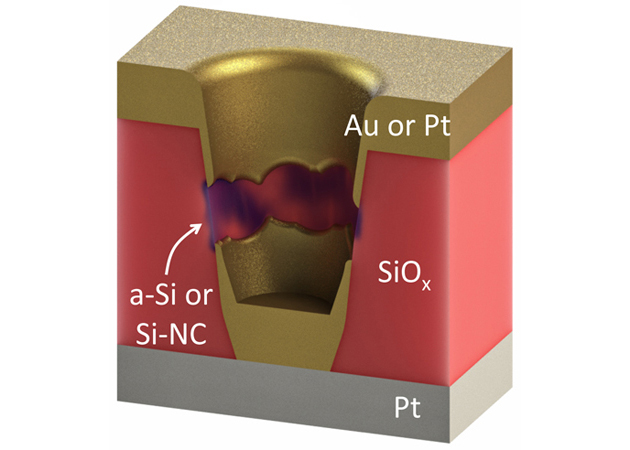

You may think that the 3GB of memory in your new smartphone is hot stuff, but that pales in comparison with what Rice University has in store. Its scientists have detailed a form ofresistive RAM (RRAM) that can be made using regular equipment at room temperatures, making it practical for everyday gadgets. The trick is the use of porous silicon oxide where metals (such as gold or platinum) fill the gaps. Using the silicon material doesn’t just give manufacturers something familiar to work with; it requires much less power than previous techniques, can last through 100 times as many uses and isn’t fazed by heat. It’s also far denser than earlier RRAM, storing nine bits per cell where even conventional flash storage stops at three. The result should be an easy-to-make RAM chip with the kind of capacity that you’d normally expect from much larger permanent storage, like an SSD — as the company Crossbar hinted when it first discussed this approach, you could stuff 1TB into a component the size of a postage stamp.

via Engadget